# Enhancing Device Performance with High Electron Mobility GeSn Materials

Yannik Junk, Omar Concepción, Marvin Frauenrath, Jingxuan Sun, Jin Hee Bae, Florian Bärwolf, Andreas Mai, Jean-Michel Hartmann, Detlev Grützmacher, Dan Buca, and Qing-Tai Zhao\*

As transistors continue to shrink, the need to replace silicon with materials of higher carrier mobilities becomes imperative. Group-IV semiconductors, and particularly GeSn alloys, stand out for their high electron and hole mobilities, making them attractive for next-generation electronics. While Ge *p*-channel devices already possess a high hole mobility, here the focus is on enhancing *n*-channel transistor performance by utilizing the superior electron mobility of GeSn as channel material. Vertical gate-all-around nanowire (GAA NW) transistors are fabricated using epitaxial GeSn heterostructures that leverage the material growth, in situ doping, and band engineering across source/channel/drain regions. It is demonstrated that increasing Sn content in GeSn alloys constantly improves the device performances, reaching a fivefold on-current improvement over standard Ge devices for 11 at.% Sn content. The present results underline the real potential of the GeSn alloys to bring performance and energy efficiency to future nanoelectronics applications.

#### 1. Introduction

The field of electronics witnesses a continuous technological development via both novel materials and innovative devices.

Y. Junk, O. Concepción, J. Sun, J. H. Bae, D. Grützmacher, D. Buca, O.-T. Zhao Peter Grünberg Institute (PGI 9) and JARA-Fundamentals of Future Information Technologies Forschungszentrum Jülich GmbH D-52428 Jülich, Germany E-mail: q.zhao@fz-juelich.de M. Frauenrath, J.-M. Hartmann CEA-LETI **MINATEC** Campus Grenoble F-38054, France F. Bärwolf, A. Mai IHP-Leibniz-Institut für innovative Mikroelektronik D-15236 Frankfurt, Germany J.-M. Hartmann University of Grenoble Alps Grenoble F-38054, France

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202400561

© 2024 The Author(s). Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/aelm.202400561

Today electronics are seamlessly integrated into our everyday lives via communications, entertainment artificial intelligence, and the Internet of Things (IoT), leading to an exponential increase in data transfer/processing and a highpower consumption.<sup>[1–3]</sup> Consequently, integrated circuits with faster speed, lower power consumption, and larger transistor integration density are a critical demand. With the classical scaling of Si-based complementary metal-oxidesemiconductor (CMOS) technology approaching its limit,<sup>[4]</sup> new semiconductors with higher carrier mobility<sup>[5]</sup> as well as novel device concepts<sup>[6-8]</sup> for low-power applications stand in the need for further nanoelectronics performance improvement.<sup>[9]</sup> By replacing the Si

channel with high-mobility semiconductors lower applied voltage can be achieved without the device's performance loss.<sup>[6]</sup> Ge is the next group IV material investigated due to its high hole mobility and compatible processes with CMOS technology.<sup>[10–12]</sup> However, its low electron mobility and limited *n*-type doping concentration restrict its performance as *n*-channel metal-oxidesemiconductor field effect transistor (MOSFET).

Group IV semiconductor alloys include a large range of alloys, extending from the binaries SiGe and GeSn to the ultimate quaternary CSiGeSn alloy, each with its specific material characteristics. The attractiveness for epitaxial growth and the subsequent fabrication of devices from these alloys is driven by the prospect of monolithic integration across varied application domains, ranging from electronics<sup>[13–19]</sup> and photonics<sup>[20–26]</sup> to thermoelectric<sup>[27,28]</sup> and spintronics<sup>[29,30]</sup> on silicon substrates. A notable advancement is achieved through the incorporation of Sn atoms into the Ge lattice, which reduces the  $\Gamma$ -valley's energy in the conduction band below that of the L-valley. This modification transforms the material from an indirect to a direct bandgap semiconductor. Such an energy band shift underscores the alloy's significant potential in photonics applications, where a fundamental direct bandgap is a property necessary for efficient light emission and absorption processes.<sup>[5,31]</sup> Moreover, the tenfold lower effective mass of the  $\Gamma$ -valley electrons compared to those of the L-valley, provides direct bandgap GeSn alloys with enhanced electron mobility,<sup>[32]</sup> particularly advantageous as channel semiconductors for MOSFETs.<sup>[13]</sup> Moreover, superior mobility facilitates improved conductivity and faster switching speeds,

#### www.advelectronicmat.de

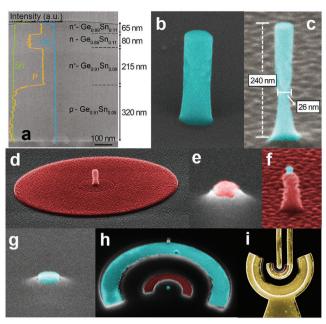

Figure 1. Device fabrication: a). TEM micrograph of one of the grown layer stacks overlaid with SIMS data showing the doping, as well as Sn and Ge contents. b) SEM image of a nanowire after RIE etching. c) SEM image of a nanowire before gate stack deposition. The nanowire's diameter is  $\approx$ 25 nm. d) After gate stack deposition and patterning. e) Exposed NW top before gate stack removal. f) NW with exposed top. g) Exposed NW top before Ni deposition. h) After via etching for gate and bottom contacts. i) Top view of the finished device with deposited contact pads. (Images d–h with false colors. Cyan: GeSn, Red: TiN, Yellow: Ti/Al.).

essential for high-performance computing applications. A hole mobility of above 500 cm<sup>2</sup> Vs<sup>-1</sup> for GeSn-channel devices outperforms Ge MOSFETs<sup>[33]</sup> and GeSn channel nanowires MOSFETs with a Sn content of only 5 at.% already led to an increase in electron mobility by a factor of 2.5 to the Ge channel device.<sup>[13]</sup> Despite promising results, most of the research on GeSn FETs has been focused on *p*-type devices, primarily because of the challenging epitaxial growth and device fabrication of high-Sn content *n*-type GeSn alloys. However, in the case of NW device architecture, the expected FET performance boost is somewhat reduced due to the limited area of the top contacts, which results in significantly high contact resistance.<sup>[34,35]</sup>

In this work, we address the previously mentioned challenges by analyzing and comparing the performance of vertical gate-allaround (GAA) nanowire (NW) *n*-type MOSFETs fabricated using direct bandgap GeSn alloys. We explore the impact of the Sn concentration on the transistor's figures-of-merit, focusing on GeSn alloys with 8 at.% Sn, marking the transition from indirect to direct bandgap, and 11 at.% Sn, which exhibits a direct bandgap.

#### 2. Layer Growth and Device Fabrication

The device design, based on GeSn/Ge heterostructure presented in **Figure 1a**, benefits significantly from the vertical nanowire (NW) architecture, which offers several key advantages: i) the source, drain, and channel regions are defined through epitaxial growth that allows precise control over the Sn content, dopant concentration, and thickness of each region. By tuning the alloy composition, the electronic band structures of every region can be tuned for specific functional requirements. ii) The doping process can be accurately controlled in situ, eliminating the need for ion implantation that introduces crystal defects, thereby reducing the injection mobility. iii) The vertical configuration decouples the device footprint from the channel length and allows for an increased device integration density. iv) The vertical design mitigates the short-channel effects that negatively impact the device performance, enhancing the overall functionality and efficiency of the semiconductor device.

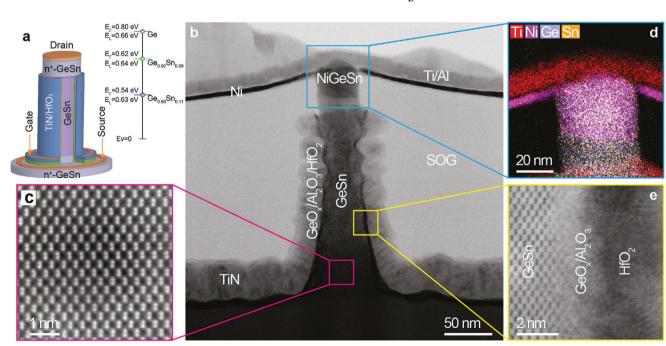

The GeSn/Ge heterostructures used for the vertical NW MOS-FETs fabrication have been epitaxially grown on Ge buffered 200 mm Si wafers using an industrial CVD reactor. Details can be found elsewhere.<sup>[36–38]</sup> The structure consists of a highly ntype phosphorus (P) doped top layer (TL), an unintentionally lowdoped middle layer (ML), and a highly *n*-doped bottom layer (BL), as summarized in Table 1. The unintentionally low-doped region defines the channel length of the device. One structure consists of constant composition  $Ge_{0.92}Sn_{0.08}$  alloy for all source, drain, and channel regions. At this Sn-concentration the bandgap is almost at the transition from indirect to direct, meaning that the  $\Gamma$ - and *L*-valley are energetically aligned<sup>[39]</sup> (see inset Figure 2a). The second GeSn heterostructure consists of a 215 nm thick  $Ge_{0.91}Sn_{0.09}$  alloy as BL (later source) and a  $Ge_{0.89}Sn_{0.11}$  alloy as channel and top layer (later drain). Based on the band structure calculations this heterostructure presents a direct bandgap through the entire device length after patterning into NW. The *n*type doping is achieved by in situ substitutional phosphorus incorporation during the GeSn epitaxy. A cross-section TEM image of the layer stack overlaid with the elemental distribution spectrum acquired via secondary ion mass spectrometry (SIMS) is shown in Figure 1a. The interface between the individual GeSn layers is free of dislocations or other crystalline defects demonstrating the high-quality of the epitaxial growth. The reference device used for comparison and for benchmarking purposes is fabricated on a n-i-n Ge homo-structure.

The GeSn NWs were fabricated using a top–down approach. First, the NWs were defined by e-beam lithography and etched by an anisotropic ICP-RIE process with a high degree of anisotropy using Cl<sub>2</sub>/Ar gas. The resulting nanowire, Figure 1b, has a height of  $\approx$ 210 nm and a diameter between 50 and 60 nm. To further reduce their diameter, the samples were subject to a cycle of oxide formation by plasma oxidation and oxide removal by HF etching. The self-limiting nature of the plasma oxidation assures high control of the diameter etching. NWs with a diameter of 25 nm were obtained as shown in the SEM image in Figure 1c.

The gate stack formation starts with the deposition of 1 nm  $Al_2O_3$  by ALD. Subsequently, a plasma post-oxidation step led to the formation of a smooth  $GeSnO_x$  layer underneath. Such a step has been shown to improve the quality of the interface and strongly reduce the interface trap density  $D_{it}$  in  $Ge.^{[40-42]}$  The gate dielectric is completed by a 5 nm HfO<sub>2</sub> layer. As a metal gate 40 nm of sputtered TiN was used and the gate pads were subsequently patterned by lithography and ICP-RIE etching (Figure 1d).

The MOSFETs fabrication continues with a planarization step and subsequent etch-back that uncovered only the top of the NW (Figure 1e) for the removal of the TiN and the dielectric (Figure 1f). A second planarization step was performed to

(1)

www.advelectronicmat.de

| Table 1. Parameters of the heterostructures used for device fabrication. |                                             |                                        |                                              |                                              |                                           |

|--------------------------------------------------------------------------|---------------------------------------------|----------------------------------------|----------------------------------------------|----------------------------------------------|-------------------------------------------|

| Device                                                                   | Top layer material                          | Top layer doping [P cm <sup>-3</sup> ] | Channel [ML]                                 | Bottom layer material                        | Bottom layer doping [P cm <sup>-3</sup> ] |

| Ge FET                                                                   | Ge 100 nm                                   | $\approx 2 \times 10^{19}$             | Ge 130 nm                                    | Ge 270 nm                                    | $\approx 2 \times 10^{19}$                |

| GeSn FET(8 at.% Sn)                                                      | Ge <sub>0.92</sub> Sn <sub>0.08</sub> 80 nm | $4 \times 10^{19}$                     | Ge <sub>0.92</sub> Sn <sub>0.08</sub> 100 nm | Ge <sub>0.92</sub> Sn <sub>0.08</sub> 200 nm | $4 \times 10^{19}$                        |

| GeSn FET(11 at.% Sn)                                                     | Ge <sub>0.89</sub> Sn <sub>0.11</sub> 65 nm | $2.5 \times 10^{19}$                   | Ge <sub>0.89</sub> Sn <sub>0.11</sub> 80 nm  | Ge <sub>0.91</sub> Sn <sub>0.09</sub> 215 nm | $3.5 \times 10^{19}$                      |

prepare the NW for top-contact formation (Figure 1g). For this purpose, 6 nm of Ni were deposited and annealed in a forming gas ambient N2:H2 to form NiGeSn metallic alloy contact. To finalize the device fabrication, vias for the gate and the bottom contacts were opened (Figure 1h) and a Ti/Al metal stack was deposited (Figure 1i).

## 3. Device Characterization

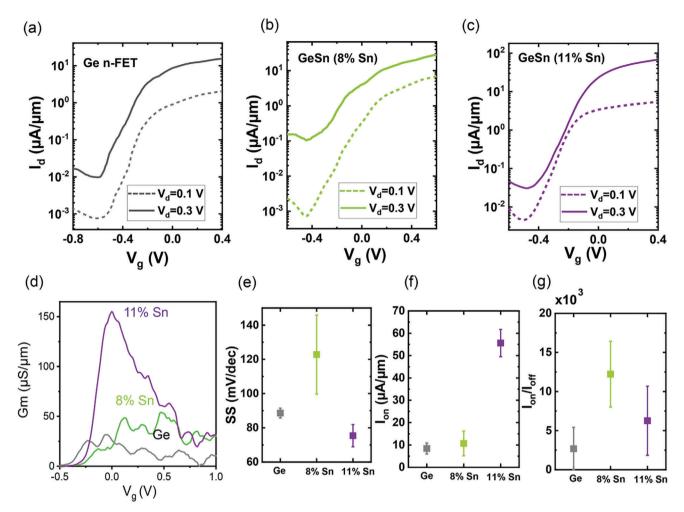

The vertical GAA NW FETs were evaluated using the bottom contact as the source and the top contact as the drain terminal. The drain current versus gate voltage (I<sub>d</sub>-V<sub>o</sub>) transfer characteristics of these devices, each with an NW diameter of 25 nm, are presented in Figure 3a-c. All devices demonstrate effective switching capabilities, characterized by a low subthreshold swing (SS) and a high on/off current ratio  $(I_{on}/I_{off})$ . The observed shift of the characteristic at a drain voltage  $V_d = 0.3$  V compared to  $V_d = 0.1 V$  is primarily attributed to an increase in the off-current at increased voltages due to gate-induced drain leakage (GIDL). Additionally, an increase in the off-current (minimum drain current) was obtained for the higher Sn content device. These results are in agreement with the lower bandgap of the GeSn layer as the Sn content increases (see inset Figure 2a). The increase in offcurrents is due to the bandgap's exponential influence on GIDL, mainly caused by band-to-band tunneling, indicating a smaller bandgap for layers with higher Sn content.

The incorporation of 8 at.% Sn into the device results in a 60% improvement in on-current, while an increase to 11 at.% Sn leads to a remarkable 410% enhancement in on-current compared to the reference Ge NW FET. This significant improvement is attributed to the enhanced electron mobility facilitated by the low effective mass of electrons in the  $\Gamma$ -valley, which becomes increasingly populated as the energy difference between the  $\Gamma$ - and Lvalleys expands with rising Sn concentration (inset of Figure 2a). This is further proved by the transconductance (G<sub>m</sub>) values, as illustrated in Figure 3d, which shows transconductance measurements of 30  $\mu$ S  $\mu$ m<sup>-1</sup> for Ge, and 52  $\mu$ S  $\mu$ m<sup>-1</sup> and 150  $\mu$ S  $\mu$ m<sup>-1</sup> for devices with 8% and 11% GeSn, respectively. The transition from a pure Ge device to a device with 11 at.% GeSn marks an approximately fivefold improvement in performance. The strong increase in transconductance highlights the improved mobility of the GeSn alloys compared to Ge. At a low V<sub>d</sub>, the maximum  $G_m$  is proportional to the intrinsic electron mobility  $\mu_0$  by:

$G_{m.max} = \frac{WC_{ox}}{L} \ \mu_0 V_d$

Figure 2. Device structure characterization. a) Schematic showing the vertical GAA GeSn NW FET architecture. The inset shows the band energy of the Γ- and L-valley at the conduction band. b) TEM micrograph of a finished device. The insets show HR-TEM micrographs of c) the lattice in the channel region, d) Elemental EDX analysis of the top part of the device underlining NiGeSn alloy on the GeSn NW, e) gate dielectric/GeSn channel interface.

SCIENCE NEWS \_\_\_\_\_

**Figure 3.** Vertical GAA GeSn NW characteristics: a–c)  $I_d-V_g$  transfer characteristics of three devices corresponding to channel materials of Ge, 8%-GeSn, and 11%-GeSn. d) Comparison of the transconductance (G<sub>m</sub>) of the devices measured at V<sub>d</sub> = 0.3 V. e–g) Comparison of subthreshold swing (SS), on-current (I<sub>on</sub>) measured at V<sub>g</sub>–V<sub>th</sub> = 0.5 V, V<sub>d</sub> = 0.3 V, and I<sub>on</sub>/I<sub>off</sub> (at V<sub>d</sub> = 0.1 V) for all three channel material devices.

where W and L correspond to the gate width and length,  $C_{ox}$  is the gate capacitance. We suggest that  $C_{ox}$  and the device dimensions W and L are the same due to the use of the same process for all devices. Hence, the only factor left to explain the improvement is the mobility. Therefore, we can conclude that the intrinsic mobility (low field mobility)  $\mu_0$  for the 11% Sn device is fivefold of the reference Ge device, demonstrating a high mobility GeSn channel for n-FETs.

The key performance indicators for the devices are summarized in Figure 3e–g. A subthreshold swing (SS) of 68 mV dec<sup>-1</sup> was recorded for a device featuring 11 at.% Sn content, closely approaching the theoretical room temperature minimum value of 60 mV dec<sup>-1</sup>. The presence of GeSnO<sub>x</sub> at the gate dielectric/GeSn channel interface has been shown to reduce the density of interface states<sup>9</sup> which significantly enhances the device electrostatic screening, thereby contributing to a low SS value. This is further reflected by the drain-induced barrier lowering (DIBL) behavior shown in the pure Ge and 8% GeSn devices. The high density of interface states in these devices causes DIBL and larger SS. The decrease of the  $I_{on}/I_{off}$  ratio with the increase in the Sn content

in the GeSn channel device is attributed to the larger GIDL due to the smaller GeSn bandgap.

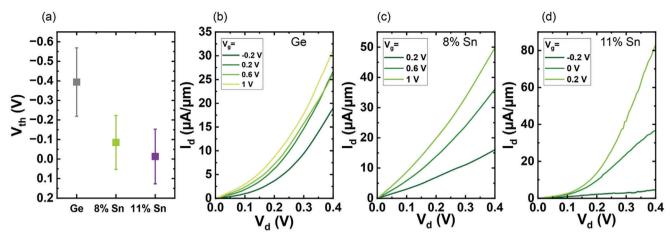

Figure 4a shows the threshold voltage  $V_{th}$ . The  $V_{th}$  is negative for all three devices. The reason for the negativity of these three values is found in the epitaxy process. During the growth of the channel layer, the CVD chamber still contains residues of the doping precursor gas from the growth of the bottom layer, leading to the incorporation of *n*-type dopants in the channel layer (Figure 1a). This causes the device to be operated like a junctionless transistor. On the other hand, intrinsic GeSn are naturally slightly *p*-type, due to the presence of crystal defects like vacancies. This *p*-type doping counteracts the incorporated *n*-type dopants. Since GeSn is an alloy, the number of vacancies and therefore the level of natural *p*-type doping is expected to be considerably higher than for the higher Sn content GeSn layer. This leads to a stronger compensation of the unintentional *n*-type doping and thereby a higher  $V_{th}$ . Another aspect to be considered is the interface quality. Judging from the SS, the interface quality is higher for the 11% GeSn alloy than for Ge and 8% GeSn. The lower  $D_{it}$  also contributes to keeping

Figure 4. a) Comparison of the  $V_{th}$  of the three devices. b–d)  $V_d-I_d$  (output) curves of the three devices: b) Ge, c) 8% GeSn, d) 11% GeSn.

the  $V_{\rm th}$  closer to zero. A third factor is the bandgap. Due to the smaller bandgap of 11% GeSn compared to Ge and 8% GeSn, a lower applied gate voltage is necessary to turn the device on. The device with 11% Sn content shows a threshold voltage close to zero, which could be suitable for low-voltage, low-power applications.

A well-known issue of *n*-type Ge(Sn) devices is the high contact resistivity and difficulty in forming Ohmic contacts. When metal is brought in contact with *n*-Ge(Sn), additional states are induced in the bandgap, so-called metal-induced gap states. In Ge(Sn), these states are very prominent close to the valence band.<sup>[43,44]</sup> In consequence, the Fermi level gets pinned close to the valence band, leading to a high Schottky barrier and a high contact resistivity on *n*-type GeSn. This phenomenon is largely independent of the work function of the metal. For vertical nanowires, the contact resistance is especially crucial, due to the extremely small size of the top contact.

Figure 4b–d shows the  $I_d$ – $V_d$  output characteristics of the three devices. It is evident that all three devices exhibit superlinear behavior, a distinctive feature characteristic of a Schottky barrier FET. While the maximum achievable *n*-type doping level of Ge is limited by insufficient dopant activation,<sup>[45]</sup> this constraint is partially relaxed for GeSn, and higher active doping concentrations can be achieved. A higher doping level is beneficial to reduce the effective Schottky barrier since it decreases the thickness of the barrier and thereby facilitates tunneling. Hence, further research into devices with improved doping levels and contact formation methods is needed to tackle this problem.

#### 4. Conclusion

In this work, we showcased the enhanced electron mobility in GeSn materials using vertical GAA NW nFETs, with significant performance gains achieved by increasing the Sn content in the channel. Specifically,  $Ge_{0.89}Sn_{0.11}$  channel devices achieved over a fivefold increase in both  $I_{on}$  and  $G_m$ , primarily through mobility enhancement. Additionally, the  $GeSnO_x$  layer at the GeSn interface contributed to a low density of interface states, achieving an SS near the theoretical minimum. The output curves still show some superlinearity, which is caused by the Schottky contact that should be addressed in future work. In conclusion, the

great potential of GeSn for nanoelectronic applications is demonstrated by the results of this work. With the continued shrinking of devices, quantum confinement will play a role in widening the bandgap in extremely aggressively scaled devices, which would alleviate the problem of high leakage current due to GIDL.

## Acknowledgements

This work was supported by the German BMBF project "SiGeSn NanoFETs" (431314977/GRK2642). This work was performed at Helmholtz Nanofacility (HNF) at Forschungszentrum Juelich.

#### **Conflict of Interest**

The authors declare no conflict of interest.

#### **Author Contributions**

The manuscript was written through contributions of all authors. All authors have given approval to the final version of the manuscript.

## **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

#### **Keywords**

direct bandgap, electron mobility, GAA nanowire MOSFET, GeSn alloy, group-IV materials

Received: July 17, 2024 Published online:

H. Pihkola, M. Hongisto, O. Apilo, M. Lasanen, Sustainability 2018, 10, 2494.

<sup>[2]</sup> S. Das, E. Mao, Sustain. Energy Grids Netw. 2020, 24, 100408.

ADVANCED SCIENCE NEWS

www.advancedsciencenews.com

ADVANCED ELECTRONIC MATERIALS

#### www.advelectronicmat.de

- [3] A. Andrae, T. Edler, Challenges 2015, 6, 117.

- [4] G. E. Moore, Proc. IEEE 1998, 86, 82.

- [5] S. Wirths, D. Buca, S. Mantl, Prog. Cryst. Growth Ch. Mater. 2016, 62, 1.

- [6] J. A. del Alamo, Nature 2011, 479, 317.

- [7] M. Liu, D. Yang, A. Shkurmanov, J. H. Bae, V. Schlykow, J.-M. Hartmann, Z. Ikonic, F. Baerwolf, I. Costina, A. Mai, J. Knoch, D. Grützmacher, D. Buca, Q.-T. Zhao, ACS Appl. Nano Mater. 2021, 4, 94.

- [8] K. J. Kuhn, IEEE Trans. Electron Devices 2012, 59, 1813.

- [9] J. D. Sau, M. L. Cohen, Phys. Rev. B 2007, 75, 045208.

- [10] D. P. Brunco, B. De Jaeger, G. Eneman, J. Mitard, G. Hellings, A. Satta, V. Terzieva, L. Souriau, F. E. Leys, G. Pourtois, M. Houssa, G. Winderickx, E. Vrancken, S. Sioncke, K. Opsomer, G. Nicholas, M. Caymax, A. Stesmans, J. Van Steenbergen, P. W. Mertens, M. Meuris, M. M. Heyns, *J. Electrochem. Soc.* **2008**, *155*, H552.

- [11] R. Pillarisetty, Nature 2011, 479, 324.

- [12] A. Toriumi, T. Nishimura, Jpn. J. Appl. Phys. 2018, 57, 010101.

- [13] M. Liu, Y. Junk, Y. Han, D. Yang, J. H. Bae, M. Frauenrath, J.-M. Hartmann, Z. Ikonic, F. Bärwolf, A. Mai, D. Grützmacher, J. Knoch, D. Buca, Q.-T. Zhao, *Comms. Eng.* **2023**, *2*, 7.

- [14] C.-P. Chou, Y.-X. Lin, Y.-K. Huang, C.-Y. Chan, Y.-H. Wu, ACS Appl. Mater. Interfaces 2020, 12, 1014.

- [15] Y.-C. Fang, K.-Y. Chen, C.-H. Hsieh, C.-C. Su, Y.-H. Wu, ACS Appl. Mater. Interfaces 2015, 7, 26374.

- [16] Y.-S. Huang, F.-L. Lu, Y.-J. Tsou, H.-Y. Ye, S.-Y. Lin, W.-H. Huang, C. W. Liu, IEEE Electron Device Lett. 2018, 39, 1274.

- [17] Y. Kang, S. Xu, K. Han, E. Y.-J. Kong, Z. Song, S. Luo, A. Kumar, C. Wang, W. Fan, G. Liang, X. Gong, *Nano Lett.* **2021**, *21*, 5555.

- [18] T. Maeda, W. Jevasuwan, H. Hattori, N. Uchida, S. Miura, M. Tanaka, N. D. M. Santos, A. Vantomme, J.-P. Locquet, R. R. Lieten, *Jpn. J. Appl. Phys.* 2015, *54*, 04DA07.

- [19] J. Zhou, G. Han, Y. Peng, Y. Liu, J. Zhang, Q.-Q. Sun, D. W. Zhang, Y. Hao, *IEEE Electron Device Lett.* 2017, 38, 1157.

- [20] B. Marzban, L. Seidel, T. Liu, K. Wu, V. Kiyek, M. H. Zoellner, Z. Ikonic, J. Schulze, D. Grützmacher, G. Capellini, M. Oehme, J. Witzens, D. Buca, ACS Photonics 2023, 10, 217.

- [21] A. Elbaz, D. Buca, N. von den Driesch, K. Pantzas, G. Patriarche, N. Zerounian, E. Herth, X. Checoury, S. Sauvage, I. Sagnes, A. Foti, R. Ossikovski, J.-M. Hartmann, F. Boeuf, Z. Ikonic, P. Boucaud, D. Grützmacher, M. El Kurdi, *Nat. Photonics* **2020**, *14*, 375.

- [22] E. Talamas Simola, V. Kiyek, A. Ballabio, V. Schlykow, J. Frigerio, C. Zucchetti, A. De Iacovo, L. Colace, Y. Yamamoto, G. Capellini, D. Grützmacher, D. Buca, G. Isella, ACS Photonics 2021, 8, 2166.

- [23] K. P. Homewood, M. A. Lourenço, Nat. Photonics 2015, 9, 78.

- [24] O. Moutanabbir, S. Assali, X. Gong, E. O'Reilly, C. A. Broderick, B. Marzban, J. Witzens, W. Du, S.-Q. Yu, A. Chelnokov, D. Buca, D. Nam, *Appl. Phys. Lett.* **2021**, *118*, 110502.

- [25] H. Tran, T. Pham, J. Margetis, Y. Zhou, W. Dou, P. C. Grant, J. M. Grant, S. Al-Kabi, G. Sun, R. A. Soref, J. Tolle, Y.-H. Zhang, W. Du, B. Li, M. Mortazavi, S.-Q. Yu, ACS Photonics 2019, 6, 2807.

- [26] J. Zheng, Z. Liu, C. Xue, C. Li, Y. Zuo, B. Cheng, Q. Wang, J. Semicond. 2018, 39, 061006.

- [27] D. Spirito, N. von den Driesch, C. L. Manganelli, M. H. Zoellner, A. A. Corley-Wiciak, Z. Ikonic, T. Stoica, D. Grützmacher, D. Buca, G. Capellini, ACS Appl. Energy Mater. 2021, 4, 7385.

- [28] O. Concepción, J. Tiscareño-Ramírez, A. A. Chimienti, T. Classen, A. A. Corley-Wiciak, A. Tomadin, D. Spirito, D. Pisignano, P. Graziosi, Z. Ikonic, Q.-T. Zhao, D. Grützmacher, G. Capellini, S. Roddaro, M. Virgilio, D. Buca, ACS Appl. Energy Mater. 2024, 7, 4394.

- [29] A. Marchionni, C. Zucchetti, F. Ciccacci, M. Finazzi, H. S. Funk, D. Schwarz, M. Oehme, J. Schulze, F. Bottegoni, *Appl. Phys. Lett.* 2021, 118, 212402.

- [30] S. de Cesari, A. Balocchi, E. Vitiello, P. Jahandar, E. Grilli, T. Amand, X. Marie, M. Myronov, F. Pezzoli, *Phys. Rev. B* 2019, *99*, 035202.

- [31] S. Gupta, B. Magyari-Köpe, Y. Nishi, K. C. Saraswat, J. Appl. Phys. 2013, 113, 073707.

- [32] K. L. Low, Y. Yang, G. Han, W. Fan, Y.-C. Yeo, J. Appl. Phys. 2012, 112, 103715.

- [33] R. Cheng, Z. Chen, S. Yuan, M. Takenaka, S. Takagi, G. Han, R. Zhang, J. Semicond. 2021, 42, 023101.

- [34] Y. Chuang, C.-Y. Liu, H.-S. Kao, K.-Y. Tien, G.-L. Luo, J.-Y. Li, ACS Appl. Electron. Mater. 2021, 3, 1334.

- [35] P. Paramahans Manik, R. Kesh Mishra, V. Pavan Kishore, P. Ray, A. Nainani, Y.-C. Huang, M. C. Abraham, U. Ganguly, S. Lodha, *Appl. Phys. Lett.* 2012, 101, 1825105.

- [36] N. von den Driesch, D. Stange, S. Wirths, D. Rainko, I. Povstugar, A. Savenko, U. Breuer, R. Geiger, H. Sigg, Z. Ikonic, J.-M. Hartmann, D. Grützmacher, S. Mantl, D. Buca, *Small* **2017**, *13*, 1603321.

- [37] O. Concepción, N. B. Søgaard, J.-H. Bae, Y. Yamamoto, A. T. Tiedemann, Z. Ikonic, G. Capellini, Q.-T. Zhao, D. Grützmacher, D. Buca, ACS Appl. Electron. Mater. 2023, 5, 2268.

- [38] N. von den Driesch, D. Stange, S. Wirths, G. Mussler, B. Holländer, Z. Ikonic, J. M. Hartmann, T. Stoica, S. Mantl, D. Grützmacher, *Chem. Mater.* 2015, *27*, 4693.

- [39] S. Wirths, R. Geiger, N. von den Driesch, G. Mussler, T. Stoica, S. Mantl, Z. Ikonic, M. Luysberg, S. Chiussi, J. M. Hartmann, H. Sigg, J. Faist, D. Buca, D. Grützmacher, *Nat. Photonics* 2015, *9*, 88.

- [40] R. Zhang, P.-C. Huang, J.-C. Lin, N. Taoka, M. Takenaka, S. Takagi, IEEE Trans. Electron. Devices 2013, 60, 927.

- [41] R. Zhang, X. Tang, X. Yu, J. Li, Y. Zhao, IEEE Electron. Device Lett. 2016, 37, 831.

- [42] R. Zhang, X. Yu, M. Takenaka, S. Takagi, *IEEE Trans. Electron Devices* 2014, 61, 2316.

- [43] T. Nishimura, K. Kita, A. Toriumi, Appl. Phys. Lett. 2007, 91, 123123.

- [44] A. Dimoulas, P. Tsipas, A. Sotiropoulos, E. K. Evangelou, Appl. Phys. Lett. 2006, 89, 252110.

- [45] R. Duffy, M. Shayesteh, I. Kazadojev, R. Yu, presented at 13th Int. Workshop on Junction Technology (IWJT), Kyoto, Japan, June 2016.