പ്പ

Abhinav Vishwakarma\*, Markus Fritscher, Amelie Hagelauer and Marc Reichenbach

# An RRAM-based building block for reprogrammable non-uniform sampling ADCs

https://doi.org/10.1515/itit-2023-0021 Received April 9, 2023; accepted April 9, 2023; published online May 4, 2023

Abstract: RRAM devices have recently seen wide-spread adoption into applications such as neural networks and storage elements since their inherent non-volatility and multi-bit-capability renders them a possible candidate for mitigating the von-Neumann bottleneck. Researchers often face difficulties when developing edge devices, since dealing with sensors detecting parameters such as humidity or temperature often requires large and power-consuming ADCs. We propose a possible mitigation, namely using a RRAM device in combination with a comparator circuit to form a basic block for threshold detection. This can be expanded towards programmable non-uniform sampling ADCs, significantly reducing both area and power consumption since significantly smaller bit-resolutions are required. We demonstrate how a comparator circuit designed in 130 nm technology can be reprogrammed by programming the incorporated RRAM device. Our proposed building block consumes 83 µW.

Keywords: ADC; CMOS circuit; comparator; memristor; non-uniform sampling; sensors.

**ACM CCS:** RRAM Device  $\rightarrow$  ADC Sensor Evaluation  $\rightarrow$  Comparator Circuit  $\rightarrow$  Memristor  $\rightarrow$  Hardware Evaluation  $\rightarrow$ System Level.

# 1 Introduction

The memristor was introduced by Leon Chua in 1971, serving as the "missing circuit element", forming the connection between the electric charge *q* and the magnetic flux  $\phi$  [1, 2]. The characteristics, among others, yield a programmable resistor, allowing to store information within these devices in a non-volatile manner. In recent years researchers have been able to demonstrate implementations of these circuit elements [3, 4]. Strukov et al. have been able to relate their implementation to the underlying memristive theory in 2008 [5]. Their implementation consists of a stack of titanium dioxide thin film (TiO<sub>2</sub>) bounded by two platinum (Pt) electrodes. The flow of electrons in that material controls the random movement of these ions in this thin film, allowing for a change of state in the device's molecular structure. The core layer works as an insulator, whereas the top film layer conducts due to the additional oxygen vacancies in the TiO<sub>2</sub> material. The resistance or state changes when the oxygen vacancies move toward the base layer; As a result, the top layer maintains a steady state [6, 7]. Since the resistance of Titanium dioxide (TiO<sub>2</sub>) can be modified it has been adopted as a component of oxygen sensors after being modified with oxygen atoms [8].

In the last years this novel device element has seen widespread adoption due to its prospective high densities and non-volatility. Recently researchers have created multiple promising circuits from these cells, including neural networks [9], memory cells [10], and radiation sensors [11].

Researchers have devised different sensors to detect physical parameters such as temperature, moisture or audio. Humidity sensors use complex mechanisms to detect the current level of moisture present within an environment [12]. Since these sensors yield an electrical parameter such as voltage or frequency, a system can use this threshold to e.g. open or close windows at a given humidity. Unfortunately, this threshold needs to be fine-tuned for a given environment and might change over a system's lifetime. A typical approach lies within using an 8-bit (or more) ADC and programming this threshold into an EEPROM. However, this yields significant implementation overhead.

We propose the approach depicted in Figure 1. We propose to utilize the programmability of the RRAM devices to

<sup>\*</sup>Corresponding author: Abhinav Vishwakarma, Brandenburgische Technische Universität, Cottbus-Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany, E-mail: abhinav.vishwakarma@b-tu.de

Markus Fritscher, Brandenburgische Technische Universität, Cottbus-Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany; and IHP - Leibniz Institute for High Performance Microelectronics, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany, E-mail: fritscher@ihp-microelectronics.com

Amelie Hagelauer, Chair of Micro- and Nanosystems Technology, Technische Universität München, Munich, Germany; and Fraunhofer EMFT Fraunhofer Institute for Electronic Microsystems and Solid State Technologies, Munich, Germany, E-mail: amelie.hagelauer@tum.de

Marc Reichenbach, Brandenburgische Technische Universität, Cottbus-Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany, E-mail: marc.reichenbach@b-tu.de

| ADC, sensor<br>evaluation,<br>neural net<br>evaluating sen-<br>sor data or ac-<br>tivations within | Comparator<br>circuit<br>swapping output<br>at programmed<br>threshold Volt- | Voltage<br>divider<br>yielding specific<br>Voltage [V] | $\begin{array}{c} \textbf{RRAM device} \\ programmed to \\ specific resis- \\ tance \left[ \Omega \right] \end{array}$ |

|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| an ANN                                                                                             | age                                                                          |                                                        |                                                                                                                        |

**Figure 1:** Proposed concept: using a RRAM device to set the threshold of a comparator allows for the easy (re)programming of a sensor evaluation circuit.

precisely set the threshold of a comparator circuit. Instead of sampling at high resolution and reading the threshold from an EEPROM we propose to use a small low-resolution non-uniform sampling ADC block consisting of one or multiple comparators. This allows to remove the highresolution ADC from the design while maintaining the programmability.

This concept can serve as the building block for a nonuniform sampling ADC if a higher quantization resolution is desired for a given application. The reprogrammability of the devices allows to adapt to sensor degradation or environmental changes during a sensor's lifetime. While the concept of using a RRAM cell within a programmable comparator has been proposed by others [13] these implementations are merely proposed as a concept, lacking both an application and an implementation using an existing and specified CMOS-Process. Within this paper we present an example implementation, consisting of a reprogrammable ADC using an optimized comparator designed using IHP<sup>1</sup> 130 nm SG13S technology, which allows for the integration of RRAM technology into CMOS designs.

The remaining paper is organized as follows: We provide an introduction into relevant topics and related work in Section 2. Section 3 provides an introduction into the implemented methodology. We evaluate the achieved results in Section 4 and conclude the paper in Section 5.

# 2 Background and related work

### 2.1 Memristor modelling

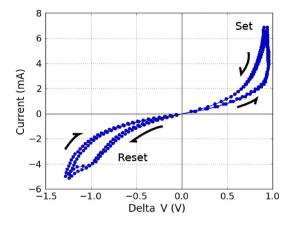

A memristor's characteristic hysteresis curve is depicted in Figure 2 [14, 15]. This curve can be generated by applying a DC signal including the devices  $V_{set}$  and  $V_{reset}$  thresholds.

An early device model has been provided by Biolek et al. [16], which is mathematically similar to [5]. The model

Figure 2: Memristor's I-V cycles hysteresis loop [14].

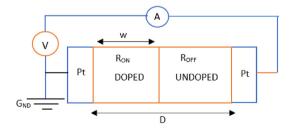

was rather simplistic, accepting only one state variable. It has been constructed as follows: The oxygen atoms doping method in TiO<sub>2</sub> thin films provides two zones with differing resistances in series with the film [16]. The doped zone  $(TiO_2 - x)$  has lower resistance and better conductivity, while the region which is not doped has higher resistance with lower conductivity. When the bias voltage is removed, the oxygen vacancies do not shift, and the region between doped and un-doped areas of the memristor's boundary remains in place [8, 17]. This is displayed by a component consisting of two resistors arranged in series  $(R_{\text{ON}}, R_{\text{OFF}} \text{ where, } R_{\text{ON}} < R_{\text{OFF}})$ . *w* represents the state variable describing each resistor's relative doped or undoped part (see Figure 3). Doped areas have an oxygen deficit  $(TiO_2 - x)$  and serve as  $R_{ON}$ , whereas undoped areas act as  $R_{\text{OFF}}$  [8].

In the following years more sophisticated models have been developed. Ding et al. provided an HSPICE Macro design for the resistive random access memory with CuxO technology (ReRAM) [18]. Pickett et al. released a more sophisticated model for the TiOx device which included nonlinear dynamics [19]. This has subsequently been implemented in SPICE [20]. Menzel et al. adapted this model to describe the electrochemical metallization memory cells

Figure 3: Memristor model based on linear ion drift titanium dioxide (HP's) [8].

<sup>1</sup> Leibniz Institute for High Performance Microelectronics.

[21]. Gao et al. have found that the observed switching behaviors of metal—oxide based RRAM can be employed to quantitatively investigate and expect the resistive switching aspects [22]. Jiang et al. have proposed the Stanford PKU model [23], which has been adapted to reflect the RRAM devices fabricated at IHP by Reuben et al. [24]. Subsequently, we chose to use it for our investigation

### 2.2 Non-uniform sampling

Henry Landau invented nonuniform sampling in 1967. This aspect of the theory of sampling deals with the Nyquist-Shannon sampling theorem's results [25]. The Shannon sampling theory for nonuniform sampling states that when an average sampling rate meets the Nyquist condition, a band-constrained signal can be rebuilt from such samples. Several hardware implementations based on this theory have been realized and the mathematical theory of nonuniform sampling thoroughly researched and recognized [26]. Later non-uniform sampling has also been used to describe non-equally distributed quantization thresholds as depicted in Figure 1. Within this paper, we will propose an efficient implementation using RRAM devices. Table 1 shows typical values obtained through nonuniform sampling. The corresponding signals obtained from the ADC interface are quantized. A range that generates the same digital signals exists among the analog input signals.

| Table 1: Regular (left) and non-uniform sampling (right) input voltages |  |

|-------------------------------------------------------------------------|--|

| lead to ADC outputs as specified.                                       |  |

| Analog<br>input (V) | Digitized<br>output | Non-uniform ADC<br>input (V) |

|---------------------|---------------------|------------------------------|

| 0                   | 00                  | 0                            |

| 0.25                | 01                  | 0.1                          |

| 0.5                 | 10                  | 0.15                         |

| 1                   | 11                  | 1                            |

Only digitized output has been bolded

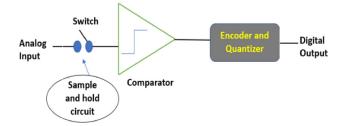

Figure 4: Operation principle of an ADC [28].

### 2.3 ADC design

Analog signals are converted into digital signals by using Analog-to-Digital Converters (ADCs) for digital signal processors in electronic devices [27]. The ADCs working principle is shown in Figure 4. The Analog signal is first sampled via a circuit (sample and hold) and changed into a discrete-time signal. The sample and hold circuit output is then quantized yielding an approximate quantization level [27, 28]. The quantization level is then encoded into a binary number. The encoded binary number becomes the output of the ADC. The rudimentary operation of the comparator lies within comparing two analog signals and outputting a 0 or 1, depending on whether input a is above or below input b. In recent times, dynamic comparators have found widespread use in reducing energy consumption and increasing the analog-to-digital signal conversion rate [29]. There are inverters in dynamic comparators that are effective at producing positive feedback. Such mechanisms can transform smaller voltage differences into more significant digital output levels. A schematic of the comparator is part of Figure 5.  $V_{\rm IP}$  is the voltage supplied at the positive terminal of the input of the comparator, and  $V_{\rm IN}$  is the negative voltage to the negative terminal [29, 30]. Suppose  $V_{\rm IP}$ , is higher than V<sub>IN</sub> in that case, the comparator outputs a binary value of 1 and 0 and vice versa.

The gain of a comparator can be written as [31]:

$$Gain = A_v = \lim_{\Delta \to 0} \frac{V_{OH} - V_{OL}}{\Delta V}$$

(1)

where  $\Delta V$  is the input voltage change  $V_{\rm IP} - V_{\rm IN}$ .  $V_{\rm OH}$  and  $V_{\rm OL}$  are defined as the high and low-level output voltage of the comparator.

The comparator's propagation delay can be expressed as follows ( $t_{rp}$  and  $t_{fp}$ , respectively, represent the rising and falling propagation delays) [31]:

$$\Delta t = \frac{t_{\rm rp} + t_{\rm fp}}{2} \tag{2}$$

Figure 5: Schematic symbol of a comparator [30].

There are different types of comparators, namely, static, static latched, dynamic, and double-tail dynamic comparators. Within this work we will focus on the static and dynamic comparators.

### 2.3.1 Static comparators

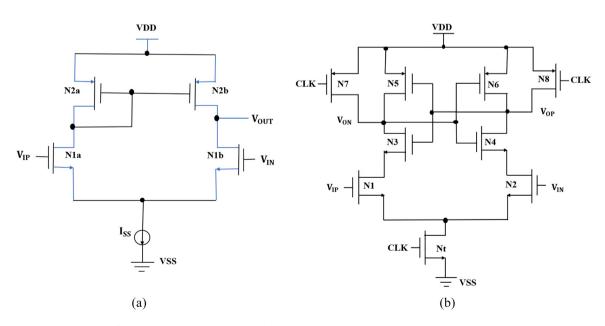

A static comparator is a basic device that compares two signals ( $V_{\rm IP}$  and  $V_{\rm IN}$ ) based on input and reference signal threshold detection. Two differential input transistors (Nla and N1b), a current mirror load (N2a and N2b), and a current source ( $I_{\rm SS}$ ) make up the traditional static comparator as depicted in Figure 6a. The input signals ( $V_{\rm IP}$ and  $V_{\rm IN}$ ) are continuously compared without being timed, regulated, or activated by any clock signals [32]. The function of a static comparator can be compared to that of an operational amplifier with compensation. A drawback of the static comparator is that it suffers from overshoots and undershoots. The circuit of the static comparator is elementary, but since it is always energized when in operation it tends to consume more power, especially at high switching speeds [32].

### 2.3.2 Dynamic comparator

The dynamic comparator typically used in high-speed ADCs is shown in Figure 6b [32]. It's operation is defined as follows: Shortly before the comparison occurs, a falling CLK signal is used to reset the comparator while turning off the

clocked transistor Nt. The pre-charged transistors N7 and N8 pull the differential outputs  $V_{\rm OP}$  and  $V_{\rm ON}$  up to VDD. During the comparison, when the clock signal rises, N7 and N8 go off, and Nt comes on [32, 33]. If  $V_{\rm IP}$  is found greater than  $V_{\rm IN}$ , the whole latch (N3, N4, N5, N6) begins a charge restoration process for  $V_{\rm ON}$  due to the charges transferred to VDD- $V_{tp}$  via the transistor N1 before  $V_{OP}$  is reduced to this voltage level and N6 turns on ahead of N5 [34]. In this moment,  $V_{\rm OP} - V_{\rm ON}$  is the amplified input voltage difference  $V_{\rm IP} - V_{\rm IN}$ . Finally,  $V_{\rm OP}$  is increased to VSS as  $V_{\rm ON}$  also reaches VDD. In case  $V_{\rm IP} < V_{\rm IN}$ , the operation of the comparator reverses. This comparator relies on vital positive feedback to perform a fast comparison. It is robust against noise and can stop the flow of current at the end of the comparison process. As a result, no static power remains in the dynamic comparator [35].

### 2.3.3 Non-uniform sampling ADC

Several non-uniform sampling ADCs have been investigated in the literature. The unique alias-free sampling property has been explored, and an ADC architecture has been provided that switches from standard voltage quantization to a hybrid quantization paradigm that uses both voltage and time quantization. The output can be used with a digital AA filter because of this mixed quantization method [36]. When the sample and hold circuit was activated, a nonuniform sampling system based on pseudo-randomness (PN) automatically created regular sampling, a lowered

Figure 6: Schematics of the static comparator (a) [32] and dynamic comparator (b) [32, 33].

sampling rate, and ADC implication for a particular input signal bandwidth [37]. A digital AA filter is an alias-free and changeable asynchronous filter algorithm approach used within the non-uniform sampling ADC architecture. The suggested filter prevents aliasing by literally processing the non-uniform samples and dynamically adjusting the filter-restored coefficients following these irregular periodic intermissions. NeuADC uses a distinct automated strategy technique with the same hardware substrate for synthesizable A/D adaptation with changeable quantization sustenance [38]. NeuADC is built on a universal NN hardware substrate using NN as inspiration and is made possible by a cutting-edge dual-path mixed-signal RRAM crossbar architecture [39].

# 3 Methodology

Within this section we describe how we constructed an optimized comparator and how we extended the circuit towards yielding a (re)programmable threshold.

### 3.1 RRAM-based comparator

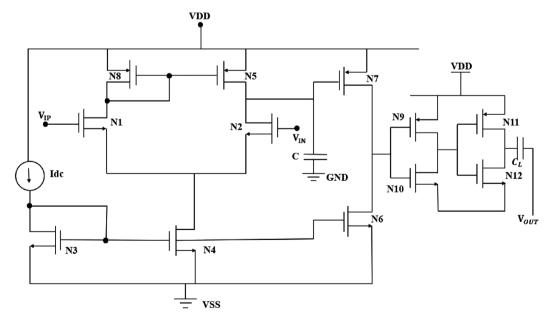

**3.1.1** Novel modified CMOS comparator design: We have depicted our proposed comparator structure in Figure 7, which is a modified two-stage CMOS comparator with the primary goal of designing a low-power, low-delay, and high-speed comparator. It consists of a differential amplifier, input stage, and an inverter output stage. The

advantage of a two-stage CMOS comparator is that the circuit requires the minimum number of transistors, ultimately resulting in reduced area consumption. The initial phase is a differential amplifier (N1, N2, N8, N5), the middle is a common-source amplifier (N4, N7), and the final is an inverter stage (N9, N10, N11, N12). The biasing circuit stage of the amplifier is accomplished with transistors (N4, N7, N6, and N3). The differential pair is connected to the two analog input voltages,  $V_{\rm ID}$ , and  $V_{\rm IN}$ . To enhance the gain of the first stage and decrease the input offset voltage, we increased the widths of the input differential pair, N1-N2. To decrease the parasitic capacitance at the N7 gate and, consequently, the propagation delay, the area of the common-source transistor was decreased. A CMOS inverter is used in the third stage, improving the comparator and adding a small amount of gain. All the other transistors act as for switching operations. The supply voltage in this circuit is 1V, while the input bias current is designed to be 50 µA. In Table 3, the dimensions of the transistors in the proposed comparator structure are presented. The circuit is designed with appropriate W/L ratios to obtain better performances in terms of delay and power. Compared to conventional architectures, the comparator power consumption and delay have improved. The key benefit of this type of comparator is that no power is wasted from the supply when the comparator is not in use. This comparator controls the leakage current on the device. It is the main advantage of this comparator, and its performance is excellent (delay) compared to those covered in refs. [35, 40, 41].

**3.1.2 Design criteria for the CMOS two stage comparator:** The positive and negative power supplies are referred to as VDD and VSS or GND, respectively. The NMOS and PMOS threshold voltages are denoted by VIP and VIN. In contrast, the transconductance parameters of NMOS and PMOS transistors are represented by  $K_n = u_n.C_{ox}$  and  $K_p = u_n.C_{ox}$ , respectively [27, 42].

Where  $C_{ox}$  = gate oxide capacitance per unit area.  $u_n$ ,  $u_v$  = signifies the electron and hole mobility.

Figure 7: Modified comparator schematic.

The process of creating a CMOS comparator has been explained by others [27, 30, 42] and is being repeated here for reference:

The gain of this stage is equivalent to the transconductance of N4 multiplied by the combined effective load resistance of the N4 and N7 output resistances. N6 serves as the load, whereas N7 requires a current to fulfill the slew rate. The current flow through  $N_7$  can be determined as follows:

$$I = C \frac{\mathrm{d}v}{\mathrm{d}t} \tag{3}$$

where *I* represents the flow of current through a capacitor, and *V* represents the voltage across it. Subsequently the Slew rate  $S_R$  can be determined as follows

$$S_R = \frac{ID_7}{C_L} \tag{4}$$

(5)

(6)

$$ID_7 = (S_R)C_L$$

Size of  $N_6$

$$\frac{N_6}{L_6} = \frac{2I_{\rm DS6}}{K_p [V_{\rm DS6}]^2}$$

Size of  $N_7$

$$\frac{N_7}{L_7} = \frac{2I_{\rm DS7}}{K_p [V_{\rm DS7}]^2} \tag{7}$$

Following the above rule, we calculated the remaining transistor size.

Gain of the first stage

$$A_{v1} = \frac{g_{n1}}{g_{n2} + g_{n5}} \tag{8}$$

Gain of the Second stage

$$A_{\nu 2} = -\frac{g_{n6}}{g_{n6} + g_{n7}} \tag{9}$$

Current values passing via N1, N2, N3, N4 and N6.

$I_{\rm DS1} = I_{\rm DS2} = I_{\rm DS3} = I_{\rm DS4} = I_{\rm DS6}.$

\* N4, ascertain the current I<sub>DS4</sub> that the mirror with N6.

$$I_{\rm DS4} = \frac{(W/L)_4}{(W/L)_6} \times I_{\rm DS6}$$

(10)

The comparator receives the biasing current from the biasing circuit. Biasing current is described in ref. [43]:

$$I_{\rm ds} = \frac{k}{2} \frac{w}{l} (V_{\rm gs} - V_{\rm th})^2 (1 + \lambda V_{\rm ds})$$

(11)

The W/L ratio is computed according to the biasing currents of the transistors.

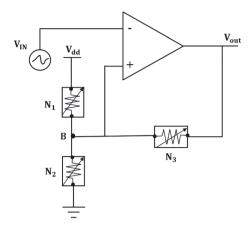

**3.1.3 Proposed RRAM based comparator:** In this section, we introduce the proposed memristor-based comparator with hysteresis, as shown in Figure 8. The application of the CMOS comparator part has been explained in the previous section. Table 2 shows the set of parameters fed to the Memristor model to simulate the behavior of the IHP's 130 nm technology RRAM cells [44]. The circuit configuration uses a voltage divider which is used to set up an upper threshold voltage  $(V_H)$  to transition below a lower threshold voltage  $(V_L)$ . The comparator input signal is applied to the inverting input. The memristor network comprising  $N_1$ ,  $N_2$ , the voltage divider, and  $N_3$  – the hysteresis level, as used in this circuit has been preprogrammed to set the hysteresis at the desired value [13]. If the supply voltage causes the output to reach

Figure 8: RRAM based comparator.

1V memristor  $N_3$  is set in parallel with memristor  $N_1$ , raising threshold voltage node B [13, 45].

This concept and the following equations have been proposed by others [13, 46], our contribution lies within adapting this to a given CMOS process and a specific RRAM device.

$$V_{H} = \frac{N_{2}}{N_{2} + \frac{N_{1}N_{3}}{N_{1} + N_{3}}} \cdot V_{dd}$$

(12)

$$V_{H} = \frac{N_2 N_3 + N_1 N_2}{N_1 N_3 + N_2 N_3 + N_1 N_2} \cdot V_{dd}$$

(13)

Similarly, when the supply voltage causes the output to reach 0 V,  $N_3$  is set in parallel with  $N_2$ , thus reducing the current to memristor  $N_2$  and the threshold voltage  $V_L$  [13, 45].

$$V_L = \frac{\frac{N_2 N_3}{N_2 + N_3}}{N_1 + \frac{N_2 N_3}{N_2 + N_2}} \cdot V_{dd}$$

(14)

$$V_L = \frac{N_2 N_3}{N_1 N_3 + N_2 N_3 + N_1 N_2} V_{dd}$$

(15)

A transition happens when the input voltage is below  $V_L$ . The following hysteresis voltage equations are derived from Equations (13) and (15) [13, 45].

$$V_H - V_L = \frac{N_2}{N_2 + \frac{N_1 N_3}{N_1 + N_2}} V_{dd}$$

(16)

$$V_H - V_L = \frac{N_1 N_2}{N_1 N_3 + N_2 N_3 + N_1 N_2} . V_{dd}$$

(17)

$$V_{dd} - V_H = V_{dd} - \left(\frac{N_3 N_2 + N_1 N_2}{N_1 N_3 + N_2 N_3 + N_1 N_2}\right) V_{dd}$$

(18)

$$V_{dd} - V_H = \frac{N_1 N_3}{N_1 N_3 + N_2 N_3 + N_1 N_2} V_{dd}$$

(19)

Table 2: RRAM model parameters as fitted by [24].

| go = 5e-10                       | Vo = 0.27 V                                            | I0 = 0.0003                                                |

|----------------------------------|--------------------------------------------------------|------------------------------------------------------------|

| vo = 0.8 m/s<br>gapini = 1.5e-10 | $\beta = 5.2$<br>$T_{o} = 300 \text{ K}$               | $\alpha = 2.1$<br>$\gamma = 22$                            |

| gapmax = 1.5e-10 $Ea = 0.6  eV$  | $t_{ox} = 6 \text{ nm}$<br>$R_{tb} = 1500 \text{ K/W}$ | $I_o = 0.003$<br>$\gamma_{\text{reset}} = 15.3 \text{ nm}$ |

Table 3: Transistor sizes/part specifictions in the circuit shown in Figure 7.

| Part | Width/length  | Part            | Width/length |

|------|---------------|-----------------|--------------|

| N1   | 0.15 μ/0.13 μ | N8              | 0.8 μ/0.13 μ |

| N2   | 0.15 μ/0.13 μ | N9              | 0.8 μ/0.13 μ |

| N3   | 0.15 μ/0.13 μ | N10             | 0.8 μ/0.13 μ |

| N4   | 0.15 μ/0.13 μ | N11             | 0.8 μ/0.13 μ |

| N5   | 0.15 μ/0.13 μ | N12             | 0.8 μ/0.13 μ |

| N6   | 0.15 μ/0.13 μ | I <sub>dc</sub> | 50 mA        |

| N7   | 0.15 μ/0.13 μ | C, C,           | 20 pf        |

The resistance of the memristors  $N_1$ ,  $N_2$  and  $N_3$  should be chosen to be very high in order to minimize the current consumption of this circuit. Equations (12) and (14) show the equations for setting the threshold voltages. We obtain the following equations from Equations (13), (15) and (17)–(15) and (19)(15) and (17)–(19)(15) and (17)–(19) [13, 45].

$$\frac{N_1}{N_3} = \frac{V_H - V_L}{V_L}$$

(20)

$$\frac{N_1}{N_2} = \frac{V_{dd} - V_H}{V_L}$$

(21)

The hysteresis threshold voltages ( $V_H$  and  $V_L$ ) are described in Equations (20) and (21), respectively.

#### 3.2 Non-uniform sampling ADC and model parameters

We can use the comparator shown earlier to implement a non-uniform ADC or a sensor evaluation circuit by stacking multiple of these blocks and having them switch at non-uniformly distributed voltages. We will demonstrate the reprogrammability within the next section.

We have used the Stanford PKU memristor model parameters as fitted by Reuben et al. [24] and as depicted in Table 2.

# **4** Evaluation

### 4.1 Comparator design

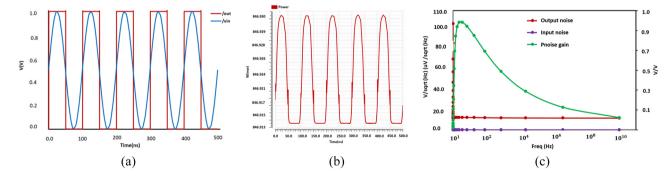

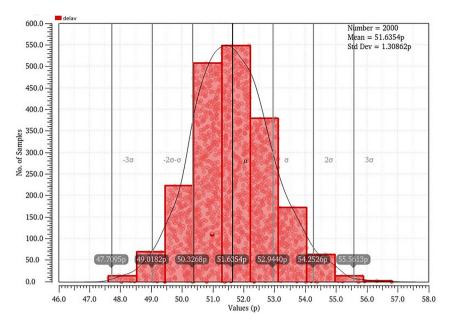

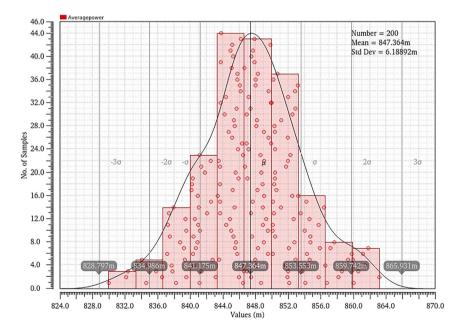

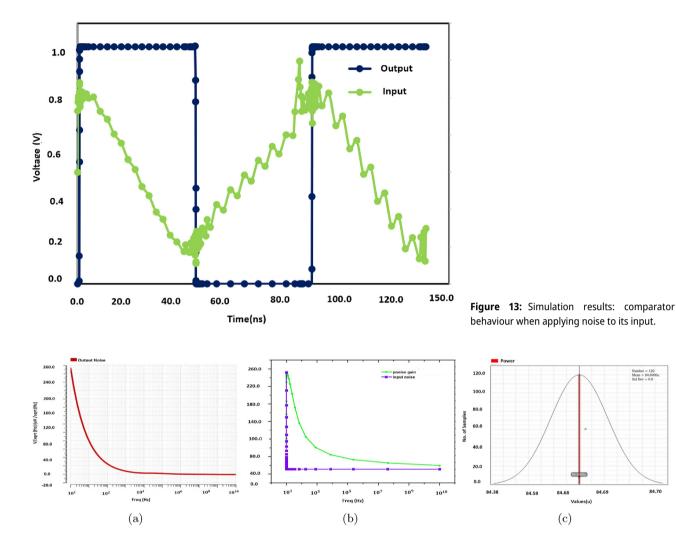

In this section, we will evaluate the proposed design as ported to the 130 nm process. We use Cadence Virtuoso to achieve the depicted simulation results. All simulations are performed considering 1V of supply voltage at  $T = 27 \degree C$ operating temperature. We used an input clock of 10 MHz with a rise and fall time of 50 ps each. The transient analysis of the proposed comparator is shown in Figure 9a. In this situation, the difference between the two inputs is 5 mv. Using the concepts described earlier the total power consumption for the proposed circuit is 8.64  $\mu$ W. Figures 10 and 11 depict Monte-Carlo simulations (2000 samples) for both power consumption and delay; The total power consumption is 847.364 mw and the standard deviation is 6.188 mw. As one can see the average delay seems to be 51.63 ps, with a standard deviation of 1.31. The dynamic power consumption variation is shown in Figure 9b. The simulation results in noise performance are shown in Figure 9c, showing the effects of input-referred noise, output noise, and phase noise margin, respectively, for the proposed comparator. The graph plot shows the relationship between Frequency (Hz) and V/sqrt referred noise (V/Hz). The merging technique, on the other hand, has been used in preamplifier transistors to increase speed and decrease the delay. The achieved specifications of the implemented comparator circuit are shown in Table 4. A comparison of the proposed comparator with designs proposed in literature is presented in Table 5. The proposed technique seems to be promising regarding delay; The power consumption is not directly comparable since this circuit is highly optimized for the specified application. The next Section will illustrate that the circuit uses way less power when integrated into the RRAM circuit.

### 4.2 Comparator RRAM optimizations

In this section we show the effectiveness of our proposed comparator design for the usage with RRAM devices. As discussed, the proposed RRAM comparator design can preserve its pre-programmed state, acting similarly to a

Figure 9: Results: transient analysis (a), corresponding power consumption (b) and noise response (c) of our design.

Figure 10: Monte Carlo simulation result for delay.

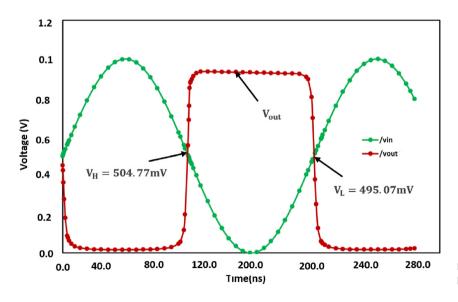

conventional resistor. Figure 12 depicts the simulation verifying the threshold voltages. The input is an ideal triangle waveform. The memristor  $N_3$  sets the hysteresis level. When the output is at a logic high (1V),  $N_3$  is in parallel with  $N_1$ . This drives more current into  $N_2$ , raising the threshold voltage ( $V_H$ ) to 504.77 mv. The input signal needs to be below  $V_H = 504.77$  mv to cause the output to transition to logic low (OV). When the output is at logic low (OV),  $N_3$  is in parallel with  $N_2$ . This reduces the current into  $N_2$ , reducing the threshold voltage to 495.07 mv. The input signal needs to increase until  $V_L = 495.07$  mv to cause the output to transition to logic low (0 V). This helps avoiding glitches when the input is slightly above or beyond the desired threshold. Figure 13 depicts the output of the

Figure 11: Monte Carlo simulation result for power consumption.

| Table 4: Parameter | specification | of the | proposed | circuit. |

|--------------------|---------------|--------|----------|----------|

|--------------------|---------------|--------|----------|----------|

| Process file           | Propsed comparator                  |  |  |

|------------------------|-------------------------------------|--|--|

| Power supply           | $Vdd = 1 V \pm 10 \%$ , $Vss = 0 V$ |  |  |

| Reference voltage      | Vref = 0-1 V                        |  |  |

| Clock signal (CLK)     | High = 1 V; low = 0 V               |  |  |

| Delay time (ps)        | 51.63                               |  |  |

| Power consumption (mw) | 846.364                             |  |  |

| Rise and fall time     | 10 ps                               |  |  |

(V/Hz). Figure 14c shows Monte-Carlo simulations (1200 samples) for power consumption of the proposed memristorbased comparator for changes in process and mismatch operations. The total power consumption is approximately 84.69  $\mu$ w with a small standard derivation of 6.2  $\mu$ w. Table 6 shows the simulated parameters of the proposed RRAM comparator.

### 4.3 Non-uniform ADC embedding RRAMs

comparator showing a single transition in spite of the noisy triangular waveform signal at its input.  $V_H$  and  $V_L$  are set to 504.77 and 495.07 mv, respectively. The output of the memristor-based comparator hysteresis ranges from 504.77 mv to 495.07 mv. The simulation results in output noise performance are shown in Figure 14a and b. These show the effects of input-referred noise and phase noise margin, respectively, for the proposed memristor-based comparator. The graph plots also show the difference between Frequency (Hz) and V/sqrt referred noise

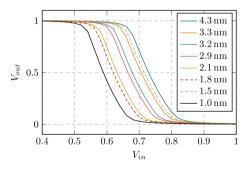

We have programmed the memristor to modify the threshold of the comparator. Since the memristors current state is modelled using the gap model variable using the employed model we use this variable to depict the current state of the device. This is equivalent to the w/d ratio depicted in Figure 3, resulting in different device resistances. The effect of different gaps on the threshold of the comparator is depicted in Figure 15. As one can see programming the RRAM device to a given gap state leads to a different threshold. Subsequently this yields a comparator with programmable threshold. Future work should investigate how device variations impact this block.

Table 5: Comparison of the proposed design with designs proposed in literature.

|                            | This work  | 2015 [40]   | 2014 [35] | 2015 [41] |

|----------------------------|------------|-------------|-----------|-----------|

| Technology CMOS (nm)       | 130        | 130         | 180       | 65        |

| Power supply (V)           | 1          | 1.2         | 1.2       | 1.2       |

| f <sub>clock</sub> (MHz)   | 10         | 1250        | 500       | 1800      |

| Delay time (ps)            | 51.63      | 17.8 ps/dec | 550       | 56 ps/dec |

| Power consumption (µW)     | 846.364 mw | 600         | 329       | 252       |

| Input referred offset (mV) | 0.5        | 7.78        | 7.8       | 5.8       |

**Figure 12:** Simulation results: comparator behaviour without noise applied to its input.

84.70

Figure 14: Output noise response (a), input and phase noise response (b), and Montecarlo simulation regarding the power consumption of the proposed comparator (c).

The programming circuit does not need to be part of the design, it can be connected externally in case a readjustment of the threshold is required. Additionally, multiple of these blocks can be combined to form a larger ADC block which is highly optimized towards the required thresholds.

Table 6: Simulated parameters of the proposed design.

| Specification             | Simulated result         |  |

|---------------------------|--------------------------|--|

| $V_H$ (upper threshold)   | 504.77 mv <u>+</u> 0.1 V |  |

| $V_{I}$ (lower threshold) | 495.07 mv ± 0.1 V        |  |

| $V_H - V_I$               | 504.77 mv-495.07 mv      |  |

| Power consumption (µW)    | 84.69 μW                 |  |

| Suply voltage             | Vdd = 1 V                |  |

Figure 15: Simulation results: programming the RRAM device to different resistances/gaps (individual colors) leads to different threshold behaviour.

# **5** Conclusions

Within this paper we have demonstrated how RRAM devices can be used to create a (re)programmable comparator by implementing this circuit using 130 nm technology. We have also elaborated how combining multiple of these blocks can form non-uniform sampling ADCs. We believe that this can help designing area and power efficient edge computing designs dealing with sensor data.

**Author contributions:** All the authors have accepted responsibility for the entire content of this submitted manuscript and approved submission.

**Research funding:** Funded by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation) – Project MIMEC Project number 441921944 as part of the DFG priority program SPP 2262 MemrisTec – Project number 422738993. **Conflict of interest statement:** The authors declare no conflicts of interest regarding this article.

# References

- L. O. Chua, "Memristor the missing circuit element," *IEEE Trans. Circ. Theor.*, vol. 18, no. 5, pp. 507–519, 1971.

- [2] K. Eshraghian, O. Kavehei, K.-R. Cho, et al., "Memristive device fundamentals and modeling: applications to circuits and systems simulation," *IEEE*, vol. 100, no. 6, pp. 1991–2007, 2012.

- [3] B. J. Choi, D. S. Jeong, S. K. Kim, et al., "Resistive switching mechanism of TiO 2 thin films grown by atomic-layer deposition," *J. Appl. Phys.*, vol. 98, no. 3, p. 033715, 2005.

- [4] D. S. Jeong, H. Schroeder, and R. Waser, "Coexistence of bipolar and unipolar resistive switching behaviors in a Pt/TiO<sub>2</sub>/Pt stack," *Electrochem. Solid State Lett.*, vol. 10, no. 8, p. G51, 2007.

- [5] D. B. Strukov, G. S. Snider, D. R. Stewart, and R. S. Williams, "The missing Memristor found," *Nature*, vol. 453, pp. 80–83, 2008.

- [6] G. Sharma and L. Bhargava, "Imply logic based on TiO<sub>2</sub> memristor model for computational circuits," in *International Conference on Circuit, Power and Computing Technologies [ICCPCT*], 2015.

- [7] S. S. Sarwar, S. A. N. Saqueb, F. Quaiyum, and A. B. M. H.-U. Rashid, "Memristor-based nonvolatile random access memory: hybrid architecture for low power compact memory design," *IEEE Access*, vol. 1, pp. 29–34, 2013.

- [8] G. Sharma and L. Bhargava, "CMOS-memristor inverter circuit design and analysis using cadence virtuoso," in *IEEE International Conference on Recent Advances and Innovations in Engineering* (*ICRAIE-2016*), Jaipur, India, 2016.

- [9] P. Yao, H. Wu, B. Gao, et al., "Fully hardware-implemented memristor convolutional neural network," *Nat. J.*, vol. 577, no. 7792, pp. 641–646, 2020.

- [10] S. R. Lee, Y.-B. Kim, M. Chang, et al., "Multi-level switching of triple-layered TaOx RRAM with excellent reliability for storage class memory," in *IEEE, Symposium on VLSI Technology (VVLSI)*, 2012, pp. 71–72.

- [11] H. Abunahla, B. Mohammad, L. Mahmoud, et al., "Memristorbased radiation sensor," *IEEE Sensor. J.*, vol. 18, no. 8, pp. 3198–3205, 2018.

- [12] Z. Chen and C. Lu, "Humidity sensors: a review of materials and mechanisms," *Sens. Lett.*, vol. 3, no. 4, pp. 274–295, 2005.

- [13] O. A. Olumodeji and M. Gottardi, "Memristor based comparator with programmable hysteresis," in *11th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME)*, IEEE, 2015, pp. 232–235.

- [14] G. A. Sanca, F. Di Francesco, N. Caroli, M. Garcia-Inza, and F. Golmar, "Design of a simple readout circuit for resistive switching memristors based on CMOS inverters," in *4th International Forum on Research and Technology for Society and Industry (RTSI)*, IEEE, 2018, pp. 1–6.

- [15] M. Barella, G. Sanca, F. G. Marlasca, et al., "LabOSat: low-cost measurement platform designed for hazardous environments," in 2016 Seventh Argentine Conference on Embedded Systems (CASE), 2016.

- [16] Z. Biolek, D. Biolek, and V. Biolkova, "SPICE model of memristor with nonlinear dopant drift," *Radioengineering*, vol. 18, no. 2, pp. 210–214, 2009.

- [17] B. Abdoli, A. Amirsoleimani, J. Shamsi, K. Mohammadi, and A. Ahmadi, "A novel CMOS-memristor based inverter circuit design," in 22 nd Iranian Conference on Electrical Engineering, 2014.

- [18] Y. Ding, X. Liu, Y. Lin, T. A. Tang, and B. Chen, "An HSPICE macromodel for resistive random access memory cell based on CuxO system," *Integrated Ferroelectrics*, vol. 96, pp. 140–145, 2008.

- [19] M. D. Pickett, D. B. Strukov, J. L. Borghetti, et al., "Switching dynamics in titanium dioxide memristive devices," *J. Appl. Phys.*, vol. 106, p. 074508, 2009.

- [20] H. Abdalla and M. D. Pickett, "SPICE modeling of memristors," in 2011 IEEE International Symposium on Circuits and Systems, 2011, pp. 1832–1835.

- [21] S. Menzel, B. Klopstra, C. Kügeler, U. Böttger, G. Staikov, and R. Waser, "A simulation model of resistive switching in electrochemical metallization memory cells," *Mater. Res. Soc. Symp. Proc.*, vol. 1160, pp. 101–106, 2009.

- [22] B. Gao, B. Sun, H. Zhang, et al., "Unified physical model of bipolar oxide-based resistive switching memory," *IEEE Electron Device Lett.*, vol. 30, pp. 1326–1328, 2009.

- [23] Z. Jiang, Y. Wu, S. Yu, et al., "A compact model for metal oxide resistive random-access memory with experiment verification," *IEEE Trans. Electron Devices*, vol. 63, no. 5, pp. 1884–1892, 2016.

- [24] J. Reuben, D. Fey, and C. Wenger, "A modeling methodology for resistive ram based on stanford-pku model with extended multilevel capability," *IEEE Trans. Nanotechnol.*, vol. 18, pp. 647–656, 2019.

- [25] H. J. Landau, "Necessary density condition of certain entire function," *Acta Math.*, vol. 117, pp. 37–52, 1967.

- [26] F. Marvasti, Nonuniform Sampling: Theory and Practice, New York, Springer Science+Business Media (Originally published by Kluwer Academic/Plenum Publishers), 2001, pp. 169–234, ISBN 978-1-4613-5451-2.

- [27] P. E. Allen and D. R. Holberg, CMOS Analog Circuit Design, New York, Oxford University Press, 2002, ISBN 0-19-511644-5.

- [28] Available at: https://microcontrollerslab.com/analog-to-digitaladc-converter-working.

- [29] S. Velagaleti, "A novel high-speed dynamic comparator with low power dissipation and low offset," M-Tech 4 thesis, NIT Rourkela, India, 2009.

- [30] S. Khan, "Design of high gain low voltage CMOS comparator," *Int. J. Res. Appl. Sci. Eng. Technol.*, vol. 6, pp. 1567–1572, 2018.

- [31] A. Majumder, M. Das, B. Nath, A. J. Mondal, and B. K. Bhattacharyya, "Design of low noise high-speed novel dynamic analog comparator in 65 nm," in *26th Conference Radio Electronics*, Slovak Republic, Kosice, 2016.

- [32] S. Huang, S. Diao, and F. Lin, "An energy-efficient high-speed CMOS hybrid comparator with reduced delay time in the 40-nm CMOS process," *Analog Integr. Circuits Signal Process.*, vol. 89, pp. 231–238, 2016.

- [33] C.-H. Chan, Y. Zhu, U. Chio, S.-W. Sin, U. Seng-Pan, and Martins, "AA reconfigurable low-noise dynamic comparator with offset calibration in 90 nm CMOS," in *IEEE Asian Solid-State Circuits Conference (A-SSCC)*, 2011, pp. 233–236.

- [34] B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and speed optimization of a latch-type voltage sense amplifier," *IEEE J. Solid State Circ.*, vol. 39, no. 7, pp. 1148–1158, 2004.

- [35] S. Babayan-Mashhadi and R. Lotfi, "Analysis and design of a low-voltage low-power double-tail comparator," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 22, no. 2, pp. 343–352, 2014.

- [36] T.-F. Wu, C.-R. Ho, and M. S.-W. Chen, "A flash based non-uniform sampling ADC with hybrid quantization enabling digital anti-aliasing filter," *IEEE J. Solid State Circ.*, vol. 52, no. 9, pp. 2335–2349, 2017.

- [37] C. A. Pappas, "A non-uniform sampling ADC: parallel digital ramp pluse position modulation," in *IEEE Canadian Conference on Electrical & Computer Engineering*, 2018.

- [38] T.-F. Wu, C.-R. Ho, and M. S.-W. Chen, "A non-uniform sampling ADC architecture with reconfigurable digital anti-aliasing filter," *IEEE Trans. Circuits Syst. I: Regul. Pap.*, vol. 63, pp. 1639–1651, 2016.

- [39] W. Cao, X. He, A. Chakrabarti, and X. Zhang, "NeuADC: Neural network-inspired RRAM-based synthesizable analog-to-digital conversion with reconfigurable quantization support," in *Design Automation & Test in Europe Conference & Exhibition (DATE)*, IEEE, 2019, pp. 1477–1482.

- [40] J. Gao, G. Li, and Q. Li, "High-speed low power common mode insensitive dynamic comparator," *Electron. Lett.*, vol. 51, no. 2, pp. 134–136, 2015.

- [41] D. Xu, S. Xu, and G. Chen, "High-speed low-power and low-power supply voltage dynamic comparator," *Electron. Lett.*, vol. 51, no. 23, pp. 1914–1916, 2015.

- [42] Sasikumar and Muthaiah, "An optimal design of CMOS two stage comparator circuit using swarm intelligence technique," *Int. J. Reconfigurable Embed. Syst.*, vol. 7, pp. 131–137, 2018.

- [43] B. Razavi, Design of Analog CMOS Integrated Circuits, Bosten, MA, McGraw-Hill, Inc., 2001.

- [44] E. P.-B. Quesada, R. Romero-Zaliz, E. Pérez, et al., "Toward reliable compact modeling of multilevel 1T-1R RRAM devices for neuromorphic systems," *Electronics*, vol. 10, p. 645, 2021.

- [45] Available at: http://www.ti.com [accessed: Apr. 06, 2023].

- [46] J. Fiorenza, R. Quan, P. Holloway, C. G. Sodini, and H. S. Lee, "Comparator-based switched-capacitor circuit for scaled CMOS technologies," *IEEE J. Solid State Circ.*, vol. 41, no. 12, pp. 2658–2668, 2006.

## **Bionotes**

#### Abhinav Vishwakarma

Brandenburgische Technische Universität, Cottbus – Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany

abhinav.vishwakarma@b-tu.de

Abhinav Vishwakarma received the B.Tech. degree in Electronics and Telecommunication Engineering from Uttar Pradesh Technical University, Lucknow, India, in 2014 and the M.Tech degree in Electronics Engineering from Madan Mohan Malaviya University of Technology, Gorakhpur, India, in 2017. He is currently pursuing a Ph.D. degree in Computer engineering with Brandenburgische Technische Universität Cottbus, Senftenberg, Germany. Before joining his Ph.D. degree, he was Research Associate in Electrical Engineering Department, Indian Institute of Technology Indore, India, from 2018 to 2019. His current research interest includes ReRAM and SRAM memory design, and Mixed-signal ICs design.

#### **Markus Fritscher**

Brandenburgische Technische Universität, Cottbus – Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany; and IHP – Leibniz Institute for High Performance Microelectronics, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

fritscher@ihp-microelectronics.com

Markus Fritscher received both a B. Sc. degree in Computational Engineering and a M. Sc degree in Computer Science at the Friedrich Alexander Universität Erlangen-Nürnberg (FAU). He is pursuing a PhD degree at BTU Cottbus-Senftenberg, Germany as part of a joint researcher position at BTU and IHP — Leibniz Institute for Microelectronics, Frankfurt (Oder). His main research interests are the development and modelling of large memristive systems, dedicated frameworks which can assist with that endeavour and HPC.

#### **Amelie Hagelauer**

Chair of Micro- and Nanosystems Technology, Technische Universität München, Munich, Germany; and Fraunhofer EMFT Fraunhofer Institute for Electronic Microsystems and Solid State Technologies, Munich, Germany amelie.hagelauer@tum.de

Amelie Hagelauer (Senior Member, IEEE) received the Dipl.-Ing. degree in mechatronics and the Dr.- Ing. degree in electrical engineering from the FAU Erlangen-Nuremberg, Germany, in 2007 and 2013, respectively. In November 2007, she joined the FAU Institute for Electronics Engineering, where she researched on BAW resonators and filters towards her Ph.D. degree. Since 2013, she has been focusing on SAW/BAW and RF MEMS components, as well as on microwave integrated circuits for frontends. From 2016 to 2019, she had been leading a Research Group on electronic circuits and from August 2019 to September 2021 she was a Full Professor at the University of Bayreuth, Germany. In September 2021, she joined the Technical University of Munich (TUM) as a Full Professor and became the Co-Director of the Fraunhofer Institute for Electronic Microsystems and Solid State Technologies EMFT, Munich. She has authored or co-authored more than 150 peer-reviewed publications in her research fields, which include research and development of microwave theory and technology, electronic circuits and systems, and communication and sensing systems. She acted as a Guest Editor for a special issue of the IEEE Transactions on Microwave Theory and Techniques on the topic RF Frontends for Mobile Radio and as an Associate Editor of the IEEE Transactions on Microwave Theory and Techniques.

#### Marc Reichenbach

Brandenburgische Technische Universität, Cottbus – Senftenberg, Computer Engineering Institute, Konrad-Wachsmann-Allee 5, 03046 Cottbus, Germany marc.reichenbach@b-tu.de

Marc Reichenbach (Member, IEEE) received the Diploma degree in computer science from Friedrich-Schiller University Jena, Germany, in 2010, and the Ph.D. degree from FriedrichAlexander University Erlangen-Nürnberg (FAU), Germany, in 2017. From 2017 to 2021, he worked as a Postdoctoral Researcher at the Chair of computer architecture, FAU. Since 2021, he has been heading the Chair of computer engineering at the Brandenburg University of Technology CottbusSenftenberg (BTU), Germany, as a Substitute Professor. His research interests include novel computer architectures, memristive computing, and smart sensor architectures for varying application fields.