#### **OPEN ACCESS**

## A 50 ps resolution monolithic active pixel sensor without internal gain in SiGe BiCMOS technology

To cite this article: G. lacobucci et al 2019 JINST 14 P11008

View the article online for updates and enhancements.

### IOP ebooks<sup>™</sup>

Bringing you innovative digital publishing with leading voices to create your essential collection of books in STEM research.

Start exploring the collection - download the first chapter of every title for free.

PUBLISHED BY IOP PUBLISHING FOR SISSA MEDIALAB

RECEIVED: September 4, 2019 ACCEPTED: October 21, 2019 PUBLISHED: November 6, 2019

# A 50 ps resolution monolithic active pixel sensor without internal gain in SiGe BiCMOS technology

G. lacobucci,<sup>*a*,1</sup> R. Cardarelli,<sup>*b*</sup> S. Débieux,<sup>*a*</sup> F.A. Di Bello,<sup>*a*</sup> Y. Favre,<sup>*a*</sup> D. Hayakawa,<sup>*a*</sup> M. Kaynak,<sup>*c*</sup> M. Nessi,<sup>*a*,*d*</sup> L. Paolozzi,<sup>*a*</sup> H. Rücker,<sup>*c*</sup> D.M.S. Sultan<sup>*a*</sup> and P. Valerio<sup>*a*</sup>

<sup>b</sup> INFN Section of Roma Tor Vergata,

Via della ricerca scientifica 1, Roma, Italy

<sup>c</sup>IHP — Leibniz-Institut für innovative Mikroelektronik,

Im Technologiepark 25, Frankfurt (Oder), Germany

<sup>d</sup>CERN,

CH-1211 Geneve 23, Switzerland

*E-mail:* giuseppe.iacobucci@unige.ch

ABSTRACT: A monolithic pixelated silicon detector designed for high time resolution has been produced in the SG13G2 130 nm SiGe BiCMOS technology of IHP. This proof-of-concept chip contains hexagonal pixels of  $65 \,\mu\text{m}$  and  $130 \,\mu\text{m}$  side. The SiGe front-end electronics implemented provides an equivalent noise charge of 90 and 160 e<sup>-</sup> for a pixel capacitance of 70 and 220 fF, respectively, and a total time walk of less than 1 ns. Lab measurements with a <sup>90</sup>Sr source show a time resolution of the order of 50 ps. This result is competitive with silicon technologies that integrate an avalanche gain mechanism.

KEYWORDS: Particle tracking detectors (Solid-state detectors); Solid state detectors; Instrumentation and methods for time-of-flight (TOF) spectroscopy; Pixelated detectors and associated VLSI electronics

ArXiv ePrint: 1908.09709

<sup>&</sup>lt;sup>a</sup>Département de Physique Nucléaire et Corpusculaire, Université de Genève,

Quai Ernest-Ansermet, Geneva, Switzerland

<sup>&</sup>lt;sup>1</sup>Corresponding author.

<sup>© 2019</sup> CERN. Published by IOP Publishing Ltd on behalf of Sissa Medialab. Original content from this work may be used under the terms of the Creative Commons Attribution 3.0 licence. Any further distribution of this work must maintain attribution to the author(s) and the title of the work, journal citation and DOI.

#### Contents

| 1 | Fast, low noise SiGe electronics and sensor design for sub-100ps timing |                                          |

|---|-------------------------------------------------------------------------|------------------------------------------|

|   | 1.1                                                                     | Introduction                             |

|   | 1.2                                                                     | Pixel matrix design                      |

|   | 1.3                                                                     | SiGe HBT based front-end                 |

| 2 | Experimental setup and calibrations                                     |                                          |

| 3 | Resu                                                                    | ılts                                     |

|   | 3.1                                                                     | Performance of the front-end electronics |

|   | 3.2                                                                     | Time resolution                          |

| 4 | Conclusions                                                             |                                          |

#### 1 Fast, low noise SiGe electronics and sensor design for sub-100ps timing

#### 1.1 Introduction

Our previous researches [1–4] proved the feasibility of a fully-efficient monolithic pixel detector in SiGe BiCMOS technology with 100 ps RMS time resolution for minimum ionising particles (MIPs). The result of [4] was obtained with a simple design that integrated the pixel matrix inside the guard-ring, while keeping the electronics in the periphery of the chip and referring the substrate to ground. The  $500 \times 500 \,\mu\text{m}^2$  area of the pixels of that chip, designed for the TT-PET project [5], was sufficient to utilise it without impacting the intrinsic resolution of positron-emission tomography. That relatively-large pixel area resulted in a pixel capacitance of 750 fF that was limiting the noise performance of the front-end. Since Cadence Spectre simulations showed that the Equivalent Noise Charge (ENC) of the preamplifier implemented in that chip decreases linearly with the pixel capacitance down to 75 fF [3], we investigated the possibility for our SiGe BiCMOS frontend to achieve time resolutions below 100 ps, even in absence of an internal gain mechanism, simply by reducing the pixel capacitance.

#### 1.2 Pixel matrix design

The reduction of the pixel capacitance requires to decrease the pixel size and reduce the signal routing distance to the preamplifier. In the prototype described here, realized in the SG13G2 130nm BiCMOS technology [6] of IHP, this is achieved by placing the electronics in triple wells inside the guard rings.

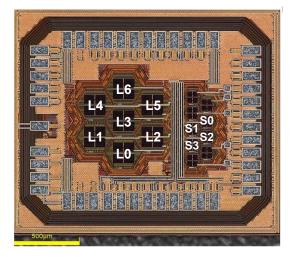

Figure 1 shows the prototype chip. It contains two matrices of hexagonal pixels with side of either 130 or 65  $\mu$ m and areas corresponding to square pixels of approximately 210 and 105  $\mu$ m, respectively. The hexagonal shape of the pixels was chosen to increase the angles at the corners of

4

**4** 4

6

8

the pixels, therefore reducing the electric field at the nearby surface and limit the risk of an early break-down due to the P-stop layer in the low-resistivity substrate. TCAD<sup>1</sup> simulations were used to estimate the pixel capacitance, which resulted to be approximately 220 fF for the large pixel and 70 fF for the small ones, for a high voltage of 140 V that provides a depletion depth of  $26 \,\mu\text{m}$ .

**Figure 1**. Photograph of the monolithic chip prototype in SG13G2 IHP technology containing two matrices of hexagonal pixels. The larger-surface matrix is made of seven pixel of  $130 \,\mu\text{m}$  side (pixels L0-L6) that share four outputs channels; pixel L3 and L5, in particular, are connected in OR to the same output driver. The second matrix, visible on the right, has nine 65  $\mu$ m-side pixels, four of which (S0-S3) are connected to the front-end. The front-end electronics is placed in the region between the two matrices.

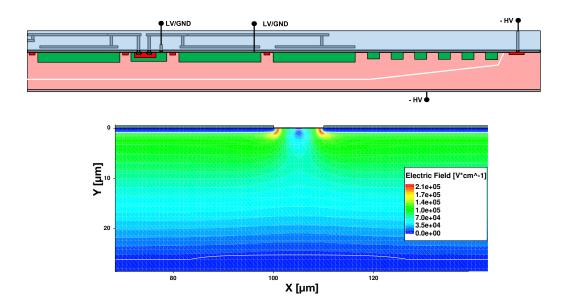

The top panel of figure 2 shows a conceptual cross section of the detector. The P-doped substrate, in the technology standard resitivity of  $50 \,\Omega \,\text{cm}$ , is connected to the negative high voltage from the top surface outside the guard-rings and from the chip backside, while the pixels and the triple wells containing the electronics are referred to the positive low-voltage. During operation, the HV connection on the chip backside is AC coupled to ground. The chip was thinned to  $60 \,\mu\text{m}$  to reduce the resistance from the backside to the limit of the depleted region, which is in series to the preamplifier input circuit. Currents below  $10 \,\text{nA} \,\text{cm}^{-2}$  were measured when the chip was operated at bias voltages up to  $140 \,\text{V}$  to take the data presented here.

Probe-station tests showed that for HV  $\approx 160$  V or larger a current rising up to 700 nA appears after two or more days of continuous operation. This current disappears if the detector is powered off for several hours. After investigations, it was realised that this effect could be due to the very high electric field inside the shallow-trench insulation at the chip surface, which is caused by the necessity to deplete a low-resistivity silicon wafer.<sup>2</sup> This current is too low to affect the noise of the pixel detector and impact its timing performance.

The depth of the depletion layer is not controlled by a backside P+ implantation, but it is limited by the low resistivity of the wafer. This solution greatly simplified the production of this proof-of-concept detector, although it slightly degrades the uniformity of the timing performance

<sup>&</sup>lt;sup>1</sup>https://www.synopsys.com/silicon/tcad.html.

<sup>&</sup>lt;sup>2</sup>This current can be eliminated by using higher-resistivity wafers that would produce a more uniform electric field.

**Figure 2**. (Top) Conceptual cross section of the monolithic pixel prototype. The P-doped regions are shown in red, while the N-doped regions in green. The white line gives an indication of the limit of the depletion region. The electronics inside the triple wells and the pixel N-well are referred to the positive low-voltage. (Bottom) TCAD simulation of the Electric field in the inter-pixel region of the sensor. The white line shows the boundary of the depletion region. The high electric field at the edge of the pixel will be reduced in future prototypes by the use of a higher-resistivity substrate.

due to the lower electric field at the boundary between two pixels. This effect is illustrated by the TCAD simulation shown in the bottom panel of figure 2.

#### 1.3 SiGe HBT based front-end

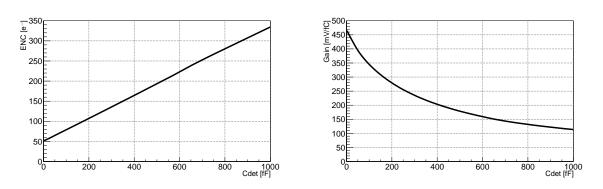

The preamplifier design is based on the one developed for the TT-PET project [3], with minor circuital adaptations to increase the gain and allow for the placement inside a deep N-well. Figure 3 shows the ENC and gain of the amplifier as predicted by Cadence Spectre simulation.

**Figure 3**. Cadence Spectre simulation of the preamplifier realised in SG13G2 IHP technology. (Left) ENC vs. detector capacitance; (Right) charge gain vs. detector capacitance. The capacitance obtained from the TCAD simulation of the large-size pixels is approximately 220 fF and that of the small pixel 70 fF.

The amplifier is DC connected to a CMOS-based open-loop 3-stage discriminator. The signal from the discriminator is sent directly to the output via a low-voltage differential driver. Both the Time Of Arrival (TOA) and the Time Over Threshold (TOT) of the amplifier output can be measured from the discriminated signal. Due to the limited number of I/Os available on the chip, the pixels share four output channels, as described in figure 1. In order to be able to turn on/off single pixels, each of them has a dedicated discrimination threshold.

#### 2 Experimental setup and calibrations

A <sup>55</sup>Fe radioactive source, that generates 5.9 keV photons, and a  $^{109}$ Cd, that generates photons of 22 keV and 25 keV relevant for this study, were used to measure the performance of the preamplifier.

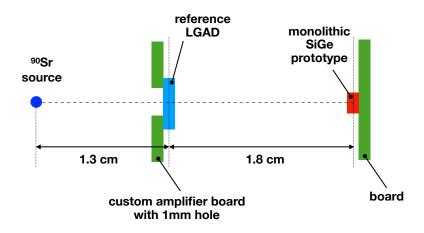

The measurement of the time resolution required the use of an LGAD detector [7] to provide a reference time. The LGAD was glued on a purposely-designed amplifier board, with a 1mmwide opening under the LGAD to let the electrons from a <sup>90</sup>Sr source reach our chip and enable a Time-Of-Flight (TOF) measurement (see figure 4). The reference LGAD used for this test has a time resolution of 50 ps RMS [7]. To verify that the time resolution of the reference LGAD is not affected by the custom amplifier board, the TOF between two LGADs was measured using the same setup. Our measurement confirmed the time resolution found in the literature.

**Figure 4**. Test setup used for the TOF measurements showing the  ${}^{90}$ Sr source, the reference LGAD glued on a purposely-designed amplifier board with a 1 mm hole to allow particles to pass through and the monolithic prototype chip under test.

#### **3** Results

#### **3.1** Performance of the front-end electronics

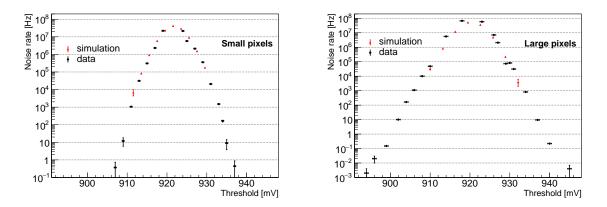

The left panel of figure 5 shows the noise hit rate of the amplifier as a function of the discriminator threshold measured in the case of the small pixel S0 of figure 1, both for a positive (above the baseline) and a negative threshold. The right panel of the same figure shows the noise hit rate for the large pixel L3. The noise hit rate measurements give an RMS voltage noise of 2.67 mV and

2.99 mV for the small and the large pixels, respectively. However, since the discriminator hysteresis acts as a filter, the actual RMS amplifier noise was obtained from Cadence Spectre simulations, and it is found to be  $\sigma_V = 4.0$  mV for the small pixels and  $\sigma_V = 4.7$  mV for the large ones.

**Figure 5**. Noise hit rate as a function of the discrimination threshold measured for (left) the small pixel S0 and (right) the large pixel L3. For thresholds below 920 mV the discrimination on the oscilloscope was done for a negative pulse slope. The red points represent the expected noise rate obtained with Cadence Spectre simulations. The large pixel shows a deviation from the Gaussian distribution of the noise at low rate values.

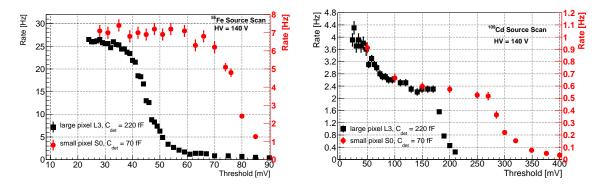

Figure 6 shows the photon hit rate as a function of the threshold measured with a <sup>55</sup>Fe and a <sup>109</sup>Cd source, for a high voltage of 140 V. The rate is approximately constant for low threshold values, indicating a good discrimination of the photon peak. The photons from the <sup>109</sup>Cd source are energetic enough to allow a rather accurate measurement of the gain, which results to be  $A_Q = 290 \text{ mV fC}^{-1}$  for the small pixel and 185 mV fC<sup>-1</sup> for the large one. Finally, from the measurement

**Figure 6.** Photon hit rate vs. discrimination threshold as obtained with (left) a  ${}^{55}$ Fe source and (right) a  ${}^{109}$ Cd source for the small pixel S0 (red dots) and for the large pixel L3 (black squares) at HV = 140 V. The offset voltage of the amplifier output is subtracted to the threshold.

of the amplifier noise and the charge gain it is possible to estimate the ENC as:

$$ENC = \frac{\sigma_V}{A_Q}$$

which gives an ENC of 90 electrons for the small pixel and 160 electrons for the large one. This results is 30% higher than the CADENCE simulation. This discrepancy, generated by the measured

values of  $A_Q$ , could be explained either by a parasitic feedback capacitance of 1.5 fF in the amplifier circuit or by a lower voltage gain of the amplifier.

#### 3.2 Time resolution

The electrons emitted by the  ${}^{90}$ Sr source were used to measure the resolution on the TOF between pixel L3 and pixel S0 of the prototype and the reference LGAD detector. For this measurement the output of the pixel under test was read by an oscilloscope with 25 Gs/s sampling rate and analogue bandwidth limited to 6 GHz. The remaining pixels were operated at low threshold and sent to a single channel of the oscilloscope to generate a tag signal for events with charge shared by the pixel under test and the neighbouring pixels. In the case of the large-pixel matrix, pixel L5, which shares the same output of L3, was masked.

Data were taken at several threshold and HV values. The TOF values were calculated as:

$$TOF = t_{hexa} - t_{LGAD}$$

where  $t_{\text{hexa}}$  is the time measured by the prototype chip and  $t_{\text{LGAD}}$  is the time measured by the reference LGAD. The selection cuts applied to the LGAD to obtain the sample used for the TOF were the same used for the verification of its 50 ps time resolution. No event selection was applied to the data of the prototype chip under test.

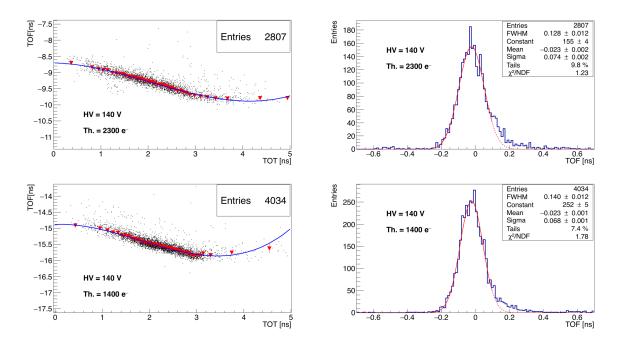

The left panels of figure 7 show the time-walk corrections obtained for the small pixel S0 and the large pixel L3 at HV = 140 V and a threshold of 1400 and 2300 electrons, respectively. The maximum time walk is found to be less than 1 ns.

The right panels of figure 7 show the TOF distribution for the same working points after time-walk correction. A non-Gaussian tail is observed for positive TOF values. This tail, present for all threshold and HV values, could be attributed to the electrons from the source crossing the region between two pixels and requires to be investigated in a testbeam. Gaussian fits to the time-walk corrected TOF distributions were performed to establish the time resolution of the core of the distributions. TOF times larger than +100 ps were excluded from the fits to avoid that the asymmetric tail alters the results. The time resolution of our monolithic prototype chip was calculated by subtraction in quadrature of the 50 ps time resolution contribution of the reference LGAD from the time-walk corrected TOF value. For the small pixel at the working point of figure 7 bottom we obtain

$$\sigma = \sqrt{\sigma_{\text{TOF}}^2 - \sigma_{\text{LGAD}}^2} = \sqrt{68^2 - 50^2} = (46 \pm 1) \,\text{ps}$$

while for the large pixel at the working point of figure 7 top the Gaussian part of the time resolution provides  $\sqrt{74^2 - 50^2} = (55 \pm 2)$  ps. In all instances the non-Gaussian tails were below 10 %. The negative mean value of the time-walk corrected TOF distributions is an artefact due to the fact that the time-walk corrections were calculated using all the events, including those in the tails.

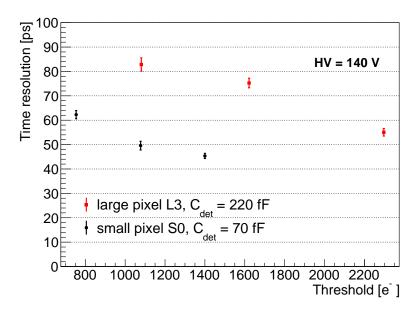

Figure 8 shows the time resolution of the prototype as a function of the discrimination threshold for the small pixel S0 and the large pixel L3 operated at HV = 140 V. For both pixel sizes the time resolution is measured to improve with increasing threshold. This observation could be explained by an improved resolution in the time-walk correction at high threshold values: the TOT, used to correct for the time walk, has a smaller error when the analogue signal crosses the discrimination

**Figure 7**. The two top panels show the data taken with the large hexagonal pixel L3 at HV = 140 V and threshold of 2300 electrons. The two bottom panels show the same information for the small pixel S0 at HV = 140 V and threshold of 1400 electrons. (Left) TOF vs. the TOT measured in the pixel. The black dots represent the events, while the red triangles the average values of the TOF distribution in each bin of TOT. These averages are used to compute the time-walk correction function shown by the blue line. The mean value of the TOF is determined by the length of the cables and it was later set to zero after time walk correction. (Right) TOF distribution after time-walk correction. The red line shows the results of the Gaussian fit performed using only the interval TOF < +100 ps, marked by the full red line. The tail of the distributions outside the Gaussian fits amounts to 9.8 % for the large pixel and to 7.4% for the small pixel.

**Figure 8**. Time resolution of the large pixel L3 (red squares) and the small pixel S0 (black dots) of the prototype monolithic detector as a function of the discrimination threshold at HV = 140 V.

threshold with a larger slope. Therefore, the present timing performance appears to be limited by the method selected to correct for the time walk.

Although the detection efficiency cannot be measured with the present experimental setup using a radioactive source, it is possible to verify that the threshold value is not cutting the measuredcharge distribution above its most-probable value. The depletion depth of a silicon sensor with bulk resistivity of 50  $\Omega$  cm operated at 140 V is 26 µm, which corresponds to a most probable deposited charge from a MIP of approximately 1600 electrons. Therefore, we should expect that in figure 8 only the two higher-threshold measurements for the large pixel suffer from a significant loss in efficiency in the detection of MIPs. For the small pixel, at the intermediate threshold value, which should be close to maximal efficiency operation, the measured time resolution is (50 ± 1) ps. For a similar threshold the large pixel shows a time resolution of (83 ± 3) ps.

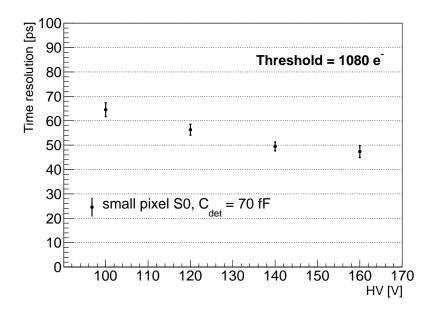

Figure 9 shows the dependence of the time resolution on the high voltage for the small pixel. An improvement of the time resolution is observed with increasing high voltage. This behaviour could be attributed to: i) an increase of the depletion region that provides a larger charge and a slightly lower capacitance, and therefore larger signal/noise; ii) a better uniformity of the carrier drift velocity. These limiting factors can be controlled by producing the sensor on a high resistivity epitaxial layer with a highly doped substrate.

**Figure 9**. Time resolution of the small pixel S0 as a function of the high voltage for a discriminator threshold of 1080 electrons.

#### 4 Conclusions

A monolithic pixel detector prototype was produced in the IHP SiGe BiCMOS SG13G2 technology, with a sensor design optimised for timing and a fast and low-noise SiGe HBT amplifier. The prototype contains small matrices of hexagonal pixels of 130 and 65  $\mu$ m side and capacitance of approximately 220 and 70 fF, respectively. Single-hit rate scans performed with a <sup>109</sup>Cd source

indicate an ENC of the preamplifier of 90 electrons RMS and a gain of  $290 \text{ mV} \text{ fC}^{-1}$  for the small pixels, and 160 electrons RMS and 185 mV fC<sup>-1</sup> for the large pixels.

Data taken with a  ${}^{90}$ Sr source were used to measure the TOF between the prototype and a reference LGAD detector that has 50 ps time resolution. A total excursion of the time walk below 1 ns was measured, which confirms the fast response of the amplifier. At a bias voltage of 140 V, time resolutions between ( $62 \pm 2$ ) ps and ( $46 \pm 1$ ) ps were measured at different thresholds for the smaller pixels after time-walk correction. These resolutions refer to the ~90% of the events in the Gaussian core of the distributions. No event selection was performed. These results are competitive with silicon technologies that integrate an avalanche mechanism, and prove that SiGe HBT technology can provide precision tracking and excellent time resolution even in the absence of an internal gain mechanism. Experiments at beamline facilities with an external tracking system will allow for more detailed studies and for an accurate measurement of the efficiency.

#### Acknowledgments

The authors wish to thank Ivan Peric for several useful discussions on the sensor integration in the CMOS process, and Nicolò Cartiglia for providing the reference LGADs used in this measurement. Special thanks go to the technical staff of the DPNC of the University of Geneva for the assembly of the instrumentation and for the support during the preparation of the test. This research is based on the work performed within the TT-PET project funded by the Swiss National Science Foundation grant CRSII2-160808.

#### References

- M. Benoit et al., 100 ps time resolution with thin silicon pixel detectors and a SiGe HBT amplifier, 2016 JINST 11 P03011 [arXiv:1511.04231].

- [2] B. Nayak, S. Krishnagopal and S. Acharya, *Beam dynamics studies of a 30 MeV RF linac for neutron production*, 2018 JINST 13 P02015.

- [3] P. Valerio et al., A monolithic ASIC demonstrator for the thin time-of-flight PET scanner, 2019 JINST 14 P07013 [arXiv:1811.10246].

- [4] L. Paolozzi et al., *Characterization of the demonstrator of the fast silicon monolithic ASIC for the TT-PET project*, 2019 *JINST* **14** P02009 [arXiv:1811.11114].

- [5] The TT-PET: thin time-of-flight PET project, SNSF grant CRSII2-160808, http://p3.snf.ch/project-160808.

- [6] H. Rucker, B. Heinemann and A. Fox, *Half-terahertz SiGe BiCMOS technology*, in 2012 IEEE 12<sup>th</sup> Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems, IEEE, (2012), pg. 129.

- [7] V. Sola et al., First FBK production of 50 µm ultra-fast silicon detectors, Nucl. Instrum. Meth. A 924 (2019) 360 [arXiv:1802.03988].

- [8] L. Paolozzi, Silicon monolithic pixel detectors in a SiGe Bi-CMOS process for sub-100 ps time resolution, oral presentation at 12<sup>th</sup> "Trento" Workshop on Advanced Silicon Radiation Detectors, FBK, Trento, Italy (2017).

- [9] C. Allaire et al., Beam test measurements of low gain avalanche detector single pads and arrays for the ATLAS high granularity timing detector, 2018 JINST 13 P06017 [arXiv:1804.00622].