# © 2017. This manuscript version is made under the CC-BY-NC-ND 4.0 license. https://doi.org/10.1016/j.mee.2017.04.003

# Assessing the forming temperature role on amorphous and polycrystalline HfO<sub>2</sub>-based 4kbit RRAM arrays performance

E. Perez<sup>1,\*</sup>, L. Bondesan<sup>2</sup>, A. Grossi<sup>2</sup>, C. Zambelli<sup>2</sup>, P. Olivo<sup>2</sup>, Ch. Wenger<sup>1</sup>

<sup>1</sup>*IHP*, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

<sup>2</sup> Università degli Studi di Ferrara, Dip. di Ingegneria, Via Saragat 1, Ferrara, 44122, Italy

\*E-mail address of corresponding author: perez@ihp-microelectronics.com

## Abstract

The impact of temperature during the forming operation on the electrical cells performance and the post-programming stability were evaluated in amorphous and polycrystalline HfO<sub>2</sub>-based arrays. Forming (between -40 and 150 °C), reset and set (at room temperature) operations were applied using the incremental step pulse with verify algorithm (ISPVA). The improvements achieved on the forming operation in terms of time and voltages reduction do not impact the subsequent reset/set results. ISPVA perturbations in LRS/HRS current distributions are almost negligible after the first reset/set operation. In this study the best improvement in forming operation in terms of yield, voltage values and cell-to-cell variability is achieved in polycrystalline samples at 80 °C.

## Keywords

RRAM, 4kbit-array, amorphous HfO<sub>2</sub>, polycrystalline HfO<sub>2</sub>, temperature impact, forming

#### **1. Introduction**

Resistive Random Access Memories (RRAM) based on  $HfO_2$  is one of the most promising technology candidates for replacing Flash memories [1]. This technology has shown high-integration density, fast low-power switching operations [2], and compatibility with CMOS processes [3]. The choice of a proper Metal-Insulator-Metal (MIM) technology for RRAM cells, exhibiting good uniformity and low switching voltages, is still a key issue for array structures fabrication and reliable electrical operation. Such a process step is mandatory to bring this technology to a maturity level.

The RRAM switching behavior is based on the electrical modification of the conductance of a MIM stack: the set operation moves the cell into a Low Resistance State (LRS), whereas reset operation brings the cell back to a High Resistance State (HRS) [4]. In order to activate the resistive switching behavior, the RRAM cells require a preliminary forming operation [3]. This initial operation plays a fundamental role in determining the subsequent devices performance [5].

In this work, the forming operation was performed at different temperatures on 4kbits arrays in order to study their impact on switching voltages, LRS/HRS current distributions and on the post programming stability.

#### 2. Experimental

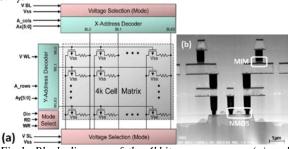

In order to ensure a reliable accuracy for statistical calculations the measurements were performed on onwafer 4kbits memory arrays (Fig. 1(a)). One complete 4kbits array was characterized at each forming temperature. The 1T-1R RRAM device is constituted by a select NMOS transistor and a resistor manufactured in 0.25 µm BiCMOS technology. The transistor also sets the current compliance. Its drain is in series to a variable resistor connected to the bitline (BL). The variable resistor is a MIM device integrated on the metal line 2 of the CMOS process. The crosssectional TEM image of the integrated RRAM cell is shown in Fig. 1(b). The MIM resistor is a  $TiN/HfO_2/Ti/TiN$  stack of 150 nm TiN layers deposited by magnetron sputtering, a 7 nm Ti layer (under TiN top electrode), and an 8 nm HfO2 layer grown by Atomic Vapor Deposition (AVD) process at low and high temperature resulting either in amorphous (A-array) and polycrystalline (P-array) HfO<sub>2</sub> films, respectively. The resistor area is equal to  $0.4 \,\mu m^2$ .

Fig.1: Block diagram of the 4kbit memory array (a) and cross-sectional TEM image of the 1T-1R integrated cell (b).

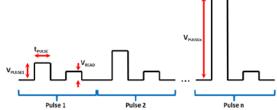

The electrical characteristics were obtained by means of a set-up based on the RIFLE SE test system working together with the Cascade PA200 semiautomatic probe system. In order to control the formation and rupture of the conductive filament (CF), the Incremental Step Pulse with Verify Algorithm (ISPVA) [6] is applied instead of a simple DC voltage sweep [7]. The ISPVA technique consists of a sequence of increasing voltage pulses (Fig. 2) on the BL during set and forming operations, whereas this sequence is applied on the source line (SL) during reset operation:  $t_{pulse} = 10 \ \mu s$ ,  $t_{fall/rise} = 1 \ \mu s$ . The amplitude of the pulses in reset and set operations ranges between  $V_{pulse} = 0.2-3 \ V$  increasing with 0.1 V, whereas in forming ranges between  $V_{pulse} = 2-5 \ V$  increasing with 0.01 V. The applied transistor gate voltage values through the wordline (WL) were 2.7 V for reset and 1.4 V for set and forming. After every pulse a Read-verify operation is performed with  $V_{WL} = 1.4$  V,  $V_{read} = 0.2$  V (applied over the BL) for 10 µs. When the Read current reaches the target value of 18 µA the set and forming operations are stopped, whereas the reset operation is stopped when the target value of 6 µA is achieved. Forming operation was performed in the temperature range from -40 to +150 °C, whereas reset and set operations were performed at room temperature.

Fig.2: Schematic illustration of the Incremental Step Pulse with Verify Algorithm (ISPVA).

### 3. Results and discussion

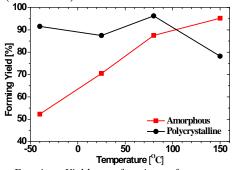

The impact of the temperature onto the forming yield (defined as the cell percentage showing a read verify current after forming above  $18\mu$ A) in A-array and P-array is illustrated in Fig. 3. The yield of the A-array shows a strong temperature dependency, the yield is increasing with raising temperature, achieving a value of about 95 % at the forming temperature 150 °C. In contrast, the yield of forming of the P-array is almost temperature independent, achieving its best value (about 96 %) at 80 °C.

*Fig.3: Forming Yield as function of temperature in Amorphous and Polycrystalline arrays.*

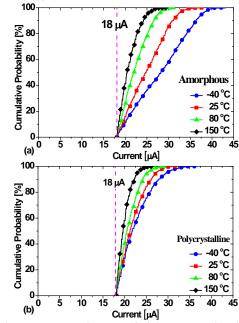

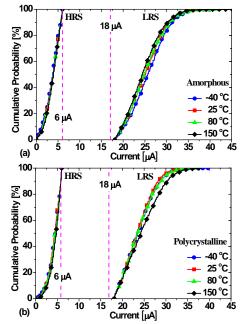

Fig. 4 shows the cumulative distributions of the currents just after the filament forming process. Although in both arrays higher temperatures lead to more compact distributions of the read-out currents, this temperature impact is more pronounced in the A-array. According to Raghavan [8] grain boundaries (GB) in polycrystalline oxides serve as a sink of oxygen vacancies to segregate to. Therefore, in the P-array the percolation path formation depends strongly on the GB distribution, whereas in the A-array the

thermal excitation in the oxide matrix plays a more fundamental role. The nMOS transistor integrated in the 1T-1R device was investigated separately in Perez et al [9]. Its results ensure that the temperature impact on the current characteristics is solely caused by the MIM resistor.

Fig.4: Current cumulative probabilities just after forming at the selected temperature values in A-arrays (a) and Parrays (b).

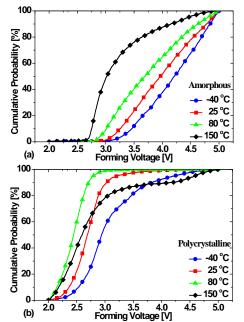

Fig. 5 illustrates the cumulative distributions of the forming voltages. The voltages required to form the cells in A-arrays decrease with temperature, but independently of the temperature these distributions remain about between 2.6 and 5 V. A similar temperature trend is shown in P-arrays below 80 °C. In contrast to the A-array, at 80 °C the number of cells formed successfully achieves almost 100 % using voltages lower than 3 V.

Fig.5: Forming voltage cumulative probabilities at the selected temperature values in A-arrays (a) and P-arrays (b).

Increasing the temperature during the forming step supports the CF formation (especially in P-arrays) and reduces the cell-to-cell variability leading to narrower current distributions [10].

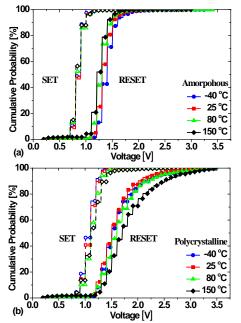

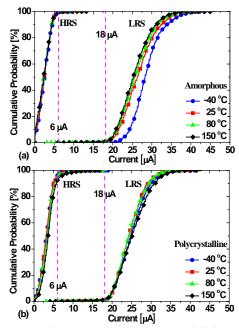

However, as shown in Fig. 6 and 7, the temperature impact found in the forming operation disappears after the first reset/set operation at room temperature. Current and voltage distributions are essentially the same regardless of the forming temperature. Therefore, the time consumption of forming operation can be strongly reduced raising temperature with no impact on the subsequent performance of the cells. The optimal conditions for the forming operation were found in P-arrays at 80 °C, providing the highest forming yield and the strongest reduction of forming voltages.

Fig.6: HRS and LRS current cumulative probabilities after reset and set operations, respectively, in A-array (a) and Parray (b).

In order to evaluate the post-programming stability, a read-out operation is performed at the end of the ISPVA forming, reset and set operations [11]. The current distributions during forming are illustrated in Fig. 8. In A-arrays and P-arrays a small number so-called cross-bit cells (cells whose current values shifted beyond the threshold value) are detected. The number of cross-bit cells is more impacted by temperature in A-arrays than in P-arrays. This result is in line with the temperature dependence of current distributions previously reported.

Fig.7: Reset and set voltage cumulative probabilities at the selected temperature, respectively, in A-arrays (a) and P-arrays (b).

Fig.8: Current cumulative probabilities at the end of ISPVA forming operation, respectively, in A-arrays (a) and P-arrays (b).

However, these ISPVA perturbations in LRS current distributions almost disappear after the first reset/set operation at room temperature, as shown in Fig. 9. For instance, a reduction of about 15 % takes place in P-arrays. In the HRS this value remains always below 5 %. Therefore, post-programming ISPVA pulses applied on the cells do not have any remarkable impact in the performance.

Fig.9: HRS and LRS current cumulative probabilities at the end of ISPVA reset and set operation, respectively, in Aarrays (a) and P-arrays (b).

## 4. Conclusions

The impact of temperature on the electrical cell performance during the forming operation has been investigated in polycrystalline and amorphous HfO<sub>2</sub>-based arrays. Increasing the temperature, the forming yield is improved, the cell-to-cell variability is reduced and the voltage values required to create the CF are smaller. After the first reset/set operation the impact of temperature and post-programmed current shift disappears, namely the switching behavior is not effectively impacted by the temperature used during the forming can be reduced by raising the temperature without any impact in the subsequent switching behavior of cells.

#### Acknowledgements

This work was supported by ENIAC Joint Undertaking 2013-2, PANACHE under Grant 621217.

### References

- H.Y. Lee, Y.S. Chen, P.S. Chen, P.Y. Gu, Y.Y. Hsu, S.M. Wang, W.H. Liu, C.H. Tsai, S.S. Sheu, P.C. Chiang, W.P. Lin, C.H. Lin, W.S. Chen, F.T. Chen, C.H. Lien, and M.-J. Tsai, "Evidence and solution of Over-RESET Problem for HfOx Based Resistive memory with Sub-ns Switching Speed and High Endurance", in Proceedings of the IEEE International Electron Devices Meeting (IEDM), pp. 19.7.1-19.7.4, 2010

- [2] H.-Y. Lee, P.-S. Chen, C.-C. Wang, S. Maikap, P.-J. Tzeng, C.-H. Lin, L.-S Lee, and M.-J. Tsai, "Low-Power Switching of Nonvolatile Resistive Memory

Using Hafnium Oxide", Jpn. J. Appl. Phys. vol. 46, pp. 2175-2179, (2007)

- [3] B. Govoreanu, G.S. Kar, Y. Chen, V. Paraschiv, S. Kubicek, A. Fantini, I.P. Radu, L. Goux, S. Clima, R. Degraeve, N. Jossart, O. Richard, T. Vandeweyer, K. Seo, P. Hendrickx, G. Pourtois, H. Bender, L. Altimine, D.J. Wouters, J.A. Kittl, and M. Jurczak, "10x10nm<sup>2</sup> Hf/HfO<sub>x</sub> crossbar resistive RAM with excellent performance, reliability and low-energy operation", in Proceedings of the IEEE International Electron Devices Meeting (Washington DC, USA), pp. 31.6.1-31.6.4, 2011

- [4] R. Waser, and M. Aono, "Nanoionics-based resistive switching memories", Nature Materials, vol. 6, pp. 833-840, 2007

- [5] G. Bersuker, D.C. Gilmer, D. Veksler, P. Kirsch, L. Vandelli, A. Padovani, L. Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti, and M. Nafría, "Metal oxide resistive memory switching mechanism based on conductive filament properties", J. Appl. Phys. vol. 110 p. 124518, 2011

- [6] A. Grossi, C. Zambelli, P. Olivo, E. Miranda, V. Stikanov, Ch. Walczyk, and Ch. Wenger, "Electrical Characterization and modeling of pulse-based forming techniques in RRAM arrays", Solid State Electron. vol. 115, pp. 17-25, 2016

- [7] E. Perez, F. Teply, and Ch. Wenger, "Electrical study of radiation hard designed HfO2-based 1T-1R RRAM devices", in Proceedings of the 2016 Materials Research Society (MRS) Fall Meeting & Exhibit, pp. 1-6, 2016

- [8] N. Raghavan, "Application of the defect clustering model for forming, SET and RESET statistics in RRAM devices", Microelectron. Reliab. vol. 64, pp. 54-58, 2016

- [9] E. Perez, Ch. Wenger, A. Grossi, C. Zambelli, P. Olivo, R. Roelofs, "Impact of temperature on conduction mechanisms and switching parameters in HfO2-based 1T-1R resistive random access memories devices", J. Vac. Sci. Technol. B vol. 35, p. 01A103, 2017

- [10] B. Butcher, G. Bersuker, K.G. Young-Fisher, D.C. Gilmer, A. Kalantarian, Y. Nishi, R. Geer, P.D. Kirsch, and R. Jammy, "Hot Forming to Improve Memory Window and Uniformity of Low-Power HfO<sub>x</sub>-Based RRAMs", in Proceedings of the IEEE IMW (Milan, Italy), pp. 1-4, 2012

- [11] A. Fantini, G. Gorine, R. Degraeve, L. Goux, C.Y. Chen, A. Redolfi, S. Clima, A. Cabrini, G. Torelli, and M. Jurczak, "Intrinsic Program Instability in HfO2 RRAM and consequences on program algorithms", in Proceedings of the IEEE International Electron Devices Meeting (Washington DC, USA), pp. 7.5.1-7.5.4, 2015