© 2018 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

DOI: 10.1109/PS.2018.8751239

# Comparison of Segmented and Traveling-Wave Electro-Optical Transmitters Based on Silicon Photonics Mach-Zehnder Modulators

Alexandru Giuglea<sup>1</sup>, Guido Belfiore<sup>1</sup>, Mahdi Khafaji<sup>1</sup>, Ronny Henker<sup>1</sup>, Despoina Petousi<sup>2</sup>, Georg Winzer<sup>2</sup>, Lars Zimmermann<sup>2</sup> and Frank Ellinger<sup>1</sup>

<sup>1</sup>Chair of Circuit Design and Network Theory, Technische Universität Dresden, 01069 Dresden, Germany

<sup>2</sup>IHP, Im Technologiepark 25, 15236 Frankfurt (Oder), Germany

Email: alexandru.giuglea@tu-dresden.de

Abstract—This paper presents a brief study of the two most commonly used topologies — segmented and traveling-wave — for realizing monolithically integrated electro-optical transmitters consisting of Si-photonics Mach-Zehnder modulators and their electrical drivers. To this end, two new transmitters employing high swing breakdown voltage doubler drivers were designed in the aforementioned topologies and compared with regard to their extinction ratio and DC power consumption at the data rate of 30 Gb/s. It is shown that for the targeted data rate and extinction ratio, a considerably lower power consumption can be achieved with the traveling-wave topology than with its segmented counterpart. The transmitters were realized in a 250 nm SiGe BiCMOS electronic-photonic integrated technology.

# I. INTRODUCTION

The ever increasing requirements regarding speed and power consumption for modern intra and inter data centers pushes the traditional electrical networks based on copper wires to their limit due to the significant losses at high frequencies. To overcome this bottleneck, optical communication is widely employed in modern network applications, as optical fibers prove to be superior to copper-made cables in terms of bandwidth and channel loss [1].

Silicon photonics technologies offer the possibility to integrate on the same silicon chip the photonic module, e.g. a photodiode or an optical modulator, and the electrical module that is supposed to drive the optical components. The key advantages of such monolithically integrated structures are the enabling of low-cost and high-yield manufacturing as well as a compact design with minimal interconnection loss.

One of the most common applications for silicon photonics technologies are electro-optical transmitters, where electrical data is to be encoded on an optical channel. To this end, voltage-controlled optical modulators are employed which modulate the electrical signal onto a continuous light wave generated by a laser. Due to their wide optical spectrum, high bandwidth and low thermal sensitivity, Mach-Zehnder modulators (MZM) are one of the most popular modulator types used in electro-optical interfaces [2].

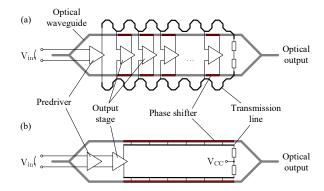

There are two common topologies for electro-optical transmitters, namely the segmented and the traveling-wave (Fig. 1).

Fig. 1. Topologies for MZM-based electro-optical transmitters: (a) Segmented; (b) Traveling-Wave.

For the former, the MZM's phase shifter (PS) is split into segments, each segment being driven by a separate driver. For the latter, there is only one single driver that drives the entire modulator, the electrodes connecting the phase shifter with the driver being modeled as transmission lines (TL). This paper makes a brief comparison of the two topologies, explaining their working principle and presenting their benefits and drawbacks. As it will be shown in Section IV, the traveling-wave (TW) approach proves to be superior to the segmented one in terms of power consumption at the targeted data rate (DR) and extinction ratio (ER).

# II. SEGMENTED TRANSMITTER TOPOLOGY

The segmented topology for electro-optical transmitters is depicted in Fig. 1 (a). The electrical driver consists of one preamplifier and several output stages, each stage driving a phase shifter segment. The purpose of the preamplifier is to align the input differential signals, while the output stage provides the actual gain of the circuit. For the output stage, a breakdown voltage doubler topology was used in order to maximize the output voltage swing, limited by the collector-emitter breakdown voltage of the bipolar transistors [3].

The main advantage of the segmented topology is that the same voltage swing is provided along the whole length of the MZM's phase shifter, with no attenuation due to long electrodes contacting the driver and the PS. Moreover, the phase shifter segment can be modeled as a lumped model consisting of a capacitor in series with a resistor [4], which does not influence the output impedance of the driver and thus its gain. On the other hand, the power consumption is high as every driver output stage consumes a high amount of power. Also, there are different propagation delays in the optical and electrical paths and special delay matching techniques have to be used [5], which further increase the complexity of the circuit. In Fig. 1 (a), meandered transmission lines connecting the preamplifier and the output stages are employed, whose group delay should match the light wave's delay in the PS segments [4].

When designing an electro-optical transmitter using a segmented topology, one has to take into consideration a series of trade-offs between extinction ratio, bandwidth and power consumption. The ER relates to both the  $V_{\pi}$ , which is the required voltage in order to get a  $180^{\circ}$  phase shift in the phase shifter, and the total length L of all phase shifter segments (the  $V_{\pi} \times L$  product is constant and denotes the electro-optical conversion efficiency [4]). The length of the PS segment is however proportional to its load capacitance  $C_L$ , which is the main constraint of the bandwidth. Finally, the number of segments is directly proportional to the overall power consumption, as each PS segment requires a separate driver output stage which needs to provide the full voltage swing.

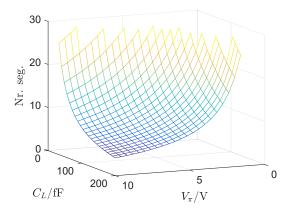

The above-mentioned trade-offs are depicted in Fig. 2, where the number of segments translates to power consumption, the load capacitance  $C_L$  to bandwidth and the  $V_\pi$  to extinction ratio. One can optimize the circuit for low power consumption (dark violet zone on the graph) by using a small number of segments; however, if a large ER is required, either long PS segments (meaning a high  $C_L$ ) or a high  $V_\pi$  is needed, which poses a challenge for the driver design. In the light yellow zone, an optimum can be found between the maximum allowed  $C_L$  for a certain bandwidth and the  $V_\pi$  that the electrical driver is able to provide, however at the cost of a very high power consumption due to the large number of segments required to ensure a high ER.

Fig. 2. Trade-offs in the design of segmented electro-optical transmitters.

The design presented in this paper was conceived for high ER (therefore the choice of a breakdown voltage doubler driver architecture capable of providing a high voltage swing) as well as for high speed. As it will be show in Section IV, the power consumption is considerable.

# III. TRAVELING-WAVE TRANSMITTER TOPOLOGY

Contrary to the segmented topology, the traveling-wave approach implies the use of one single electrical driver and long transmission lines to connect the driver to the phase shifter. This topology presents several advantages in comparison with its segmented counterpart. Firstly, the large capacitive load of the PS, which is the main limitation of the bandwidth, is canceled out by the inductive impedance of the TL (which in turn provides additional inductive peaking, thus improving the bandwidth). Secondly, the delays in the optical and electrical paths tend to match naturally [5], the mismatch being easily adjusted by changing the width of the TL. Thirdly, a smaller power consumption can be achieved as only one driver output stage is driving the MZM. However, the TL's characteristic impedance, which is further decreased when loaded with the capacitive impedance of the PS, has a negative impact on the driver's gain. Another drawback of the TW topology is the attenuation of the signal in the electrical path due to the non-zero resistance of the TL, which further increases at high frequencies due to the skin effect.

When designing a TW electro-optical transmitter, special care has to be given to the modeling of the transmission line. One has to ensure both matching at the TL's end by means of termination resistors to avoid signal reflections, as well as delay matching in the optical and electrical paths. To this end, two variables serve to model the *loaded* TL, namely the characteristic impedance  $Z_0$  and the propagation delay t [6]:

$$Z_0 = \sqrt{\frac{L_0}{C_0 + C_L}}$$

(1)  $t = \sqrt{L_0 \cdot (C_0 + C_L)}$  (2)

where  $L_0$  and  $C_0$  are the TL's inductance and capacitance per unit of length and  $C_L$  the phase shifter's load capacitance per unit of length.

For the TW transmitter presented in this paper, the TL was designed with an as high as possible  $L_0$  in order to maximize the TL's characteristic impedance and thus the electrical driver's gain. The driver topology is the same as for the segmented transmitter with the sole difference that the output stage was designed as an open-collector, using the impedance of the transmission line itself as load. This choice makes the driver highly adaptable in terms of MZM load that it can drive.

# IV. MEASUREMENT AND SIMULATION RESULTS

The electrical drivers for each topology were realized in a 250 nm SiGe BiCMOS electronic-photonic integrated technology. For the electro-optical simulations, a Verilog-A model of the MZM was used.

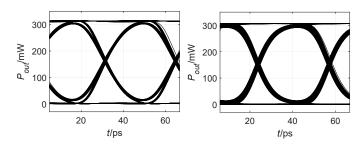

The simulated optical output eye diagrams for the two transmitter topologies are depicted in Fig. 3. In both simulations,

Fig. 3. Simulated optical output eye diagrams at 30 Gb/s for segmented (left) and traveling-wave (right) topology.

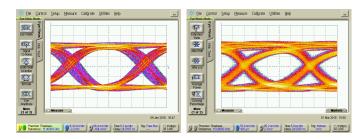

Fig. 4. Measured electrical output eye diagrams at 30 Gb/s for segmented (left) and traveling-wave (right) driver topology. The equivalent vertical scales considering the 10 dB (for segmented) and 20 dB (for TW) attenuators are 0.29 V/div and 0.78 V/div, respectively.

an MZM with 3.6 mm long phase shifters was considered. The maximum voltage swing that can be provided by the driver of each topology is 7.6  $V_{pp,diff}$ . For the segmented topology, a number of 10 phase shifter and driver segments was implemented targeting a high extinction ratio at high data rates, however at the cost of a high power consumption.

The electrical drivers were realized based on the simulation results of the electro-optical transmitter. The measurement results for the segmented and the TW driver are displayed in Fig. 4. For the segmented driver it was not possible to measure the full voltage swing because the driver's output impedance was lowered due to the  $50~\Omega$  impedance of the sampling

TABLE I

STATE-OF-THE-ART COMPARISON OF SI-PHOTONICS MZM

TRANSMITTERS (OOK MODULATION)

|                      | DR<br>(Gb/s) | Out.<br>Swing<br>(V <sub>pp,d</sub> ) | P <sub>DC</sub> (W) | ER<br>(dB) | PS<br>Length<br>(mm) | Topol-<br>ogy | Tech.            |

|----------------------|--------------|---------------------------------------|---------------------|------------|----------------------|---------------|------------------|

| [7]                  | 25           | 5                                     | 0.275               | 6.1        | 3                    | Seg.          | 65 nm<br>CMOS    |

| [5]                  | 25           | 6.4                                   | 0.52                | 4.1        | 1.5                  | TW            | 65 nm<br>CMOS    |

| [4]                  | 28           | 4                                     | 2                   | 13         | 6.08                 | Seg.          | 250 nm<br>BiCMOS |

| [6]                  | 50           | 4                                     | 0.45                | 2.7        | 3.36                 | TW            | 130 nm<br>BiCMOS |

| [8]                  | 56           | 1.6                                   | 0.3                 | 2.5        | 3.15                 | TW            | 55 nm<br>BiCMOS  |

| This<br>Work<br>Seg. | 30           | 7.6                                   | 6.4                 | 12.2       | 3.6                  | Seg.          | 250 nm<br>BiCMOS |

| This<br>Work<br>TW   | 30           | 7.6                                   | 1.5                 | 12.9       | 3.6                  | TW            | 250 nm<br>BiCMOS |

oscilloscope. For both measurements, attenuators have been used in order to avoid damage to the oscilloscope due to the high output swing.

Table I contains the performance summary and the comparison with the state-of-the-art for the two transmitter topologies.

For the data rate of 30 Gb/s, the segmented and the TW topologies show comparable performance in terms of ER. However, the TW topology consumes a significantly lower amount of power in comparison with the segmented one thanks to its electrical driver consisting of only one single output stage. Thus, for the chosen MZM's phase shifter length and for the targeted DR and ER, the TW topology provides a significantly better performance in terms of power consumption than its segmented counterpart.

# V. CONCLUSION

This paper presents a brief comparison of a segmented and a traveling-wave electro-optical transmitter designed for high data rates and high extinction ratio. For each topology we described the functioning principle and the design trade-offs. We have shown that for the targeted DR and ER, the traveling-wave approach proves superior to the segmented one in terms of power consumption due to the electrical driver and the electro-optical interface architecture.

# ACKNOWLEDGMENT

This work is funded under Photonics PPP from the EU's H2020 RIA programme in project DIMENSION (grant 688003).

# REFERENCES

- B. Razavi, Design of Integrated Circuits for Optical Communications. McGraw-Hill, 2003.

- [2] H. Xu, X. Li, X. Xiao, Z. Li, Y. Yu, and J. Yu, "Demonstration and characterization of high-speed silicon depletion-mode Mach-Zehnder modulators," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, no. 4, pp. 23–32, July 2014.

- [3] S. Mandegaran and A. Hajimiri, "A breakdown voltage multiplier for high voltage swing drivers," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 2, pp. 302–312, Feb 2007.

- [4] P. Rito, I. G. López, D. Petousi, L. Zimmermann, M. Kroh, S. Lischke, D. Knoll, D. Micusik, A. Awny, A. C. Ulusoy, and D. Kissinger, "A monolithically integrated segmented linear driver and modulator in EPIC 0.25-μm SiGe:C BiCMOS platform," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 20, no. 4, pp. 23–32, Dec 2016.

- [5] N. Qi, X. Xiao, S. Hu, X. Li, H. Li, L. Liu, Z. Li, N. Wu, and P. Y. Chiang, "Co-design and demonstration of a 25-Gb/s silicon-photonic Mach-Zehnder modulator with a CMOS-based high-swing driver," *IEEE Journal of Selected Topics in Quantum Electronics*, vol. 22, no. 6, pp. 131–140, Nov 2016.

- [6] G. Denoyer, C. Cole, A. Santipo, R. Russo, C. Robinson, L. Li, Y. Zhou, J. Chen, B. Park, F. Boeuf, S. Crmer, and N. Vulliet, "Hybrid silicon photonic circuits and transceiver for 50 Gb/s NRZ transmission over single-mode fiber," *Journal of Lightwave Technology*, vol. 33, no. 6, pp. 1247–1254, March 2015.

- [7] M. Cignoli, G. Minoia, M. Repossi, D. Baldi, A. Ghilioni, E. Temporiti, and F. Svelto, "A 1310nm 3D-integrated silicon photonics Mach-Zehnder-based transmitter with 275mW multistage CMOS driver achieving 6dB extinction ratio at 25Gb/s," in 2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers, Feb 2015, pp. 1–3.

- [8] E. Temporiti, G. Minoia, M. Repossi, D. Baldi, A. Ghilioni, and F. Svelto, "A 56Gb/s 300mW silicon-photonics transmitter in 3D-integrated PIC25G and 55nm BiCMOS technologies," in 2016 IEEE International Solid-State Circuits Conference (ISSCC), Jan 2016, pp. 404–405.