"© 2015 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works."

# Impact of inter-cell and intra-cell variability on forming and switching parameters in RRAM arrays

Alessandro Grossi, Damian Walczyk, Member, IEEE, Cristian Zambelli, Member, IEEE, Enrique Miranda, Senior Member, IEEE, Piero Olivo, Valeriy Stikanov, Alessandro Feriani, Jordi Suñé, Fellow, IEEE, Gunter Schoof, Rolf Kraemer, Bernd Tillack, Alexander Fox, Thomas Schroeder, Christian Wenger, and Christian Walczyk

Abstract—The inter-cell variability of the initial state and the impact of d.c. and pulse forming on inter-cell variability as well as on intra-cell variability in TiN/HfO2/Ti/TiN 1T-1R devices in 4 kbit memory arrays were investigated. Nearly 78% of devices on particular arrays were d.c. formed with a wordline voltage  $V_{WL}$  = 1.4 V and a bitline voltage  $V_{BL} = 2.3$  V, whereas 22% devices were not formed due to the combined effect of the extrinsic processinduced inter-cell variability of the initial state and intrinsic intercell variability after d.c. forming. Furthermore, pulse-induced forming with pulse widths on the order of 10  $\mu$ s (V<sub>WL</sub> = 1.4 V,  $V_{BL} = 3.5$  V) caused for 86% of devices a low resistance state. Using a retry algorithm, we achieve 100 % of formed devices. To assess and confirm the nature of the variability during forming operation and during cycling the quantum point-contact (QPC) model was considered. The modeling results demonstrate a relationship between the forming and the device performance. The cells requiring large energy for forming operation, due to impurities in the HfO<sub>2</sub> deposition during array processing, are those subject to poor switching performance, larger variability, and faster wear-out. Devices formed by pulse-retry algorithm show (i) shorter endurance and (ii) higher variability during cvcling.

*Index Terms*—4 kbit RRAM array, Inter-cell variability, Intracell variability, Hafnium dioxide (HfO<sub>2</sub>), Pulse-induced forming, Quantum point-contact (QPC) model.

## I. INTRODUCTION

**R** ECENT advances in the performance of resistive random access memory (RRAM) have led to significant interest in system-on-chip applications in Si-based CMOS technologies, in particular for microcontrollers in wireless sensor nodes and in automotive electronics [1], [2]. For sensor nodes, the integration of energy-efficient microcontrollers with RRAM could provide the prospect of completely autonomous systems. In electric cars, energy-efficient microcontrollers for internal states storage in complex control units are inevitable due

D. Walczyk, G. Schoof, R. Kraemer, B. Tillack, A. Fox, T. Schroeder, Ch. Wenger, and Ch. Walczyk are with IHP, 15236 Frankfurt (Oder), Germany (e-mail: walczykd@ihp-microelectronics.com).

C. Zambelli, A. Grossi, and P. Olivo are with the Department Ingegneria ENDIF, Universitá degli Studi di Ferrara, Via G. Saragat, 44122 Ferrara, Italy.

E. Miranda and J. Suñé are with the Departament d'Enginyeria Electrónica, Universitat Autónoma de Barcelona, Campus UAB, Cerdanyola del Valles, 08193 Barcelona, Spain.

V. Stikanov is with IASA, 37 Prospect Peremogy, 03056 Kiev, Ukraine.

A. Feriani is with NplusT Semiconductor Application Center, Via Umbria 112, 06132 San Martino in Colle (PG), Italy.

B. Tillack is also with the Department of Computer Engineering and Microelectronics, Technische Universität Berlin, 10587 Berlin, Germany.

R. Kraemer and T. Schroeder are also with the Brandenburgische Technische Universität, Konrad-Zuse-Strasse 1, 03046 Cottbus, Germany.

to the relatively low energy supply resources. Hence, recent hardware-based approaches focus on the integration of HfO2based RRAM in a microcontroller unit [3]. HfO<sub>2</sub> is one of the most promising transition metal oxides for RRAM with an ideal CMOS back-end-of-line compatibility. Thus considerable progress has been made in 1T-1R device integration as well as in understanding the physical/chemical properties of the resistance change behavior. Although memory arrays in the 1T-1R architecture demonstrated excellent performance parameters [4]–[7], the inter-cell variability (variations between cells) and intra-cell variability (cycle-to-cycle variations of any given cell) still prevents RRAM manufacturing from fast commercialization. While the intra-cell variability can be optimized for the particular memory cells, the inter-cell variability in memory arrays must be minimized [8]. Hence, several investigations on the extrinsic process-induced and intrinsic microscopic origin of the inter-cell and intra-cell variability after forming have been carried out in the recent past [9]-[14]. In this work, however, we first investigate the inter-cell variability of the initial state in memory arrays and then study the impact of d.c. and pulse forming on inter-cell variability as well as on intra-cell variability. To assess and confirm the nature of the variability during forming operation and during cycling the quantum point-contact (QPC) model was considered.

### **II. DEVICES AND EXPERIMENTS**

The bottom metal electrode of 150 nm TiN with a sheet resistance of 10-50  $\Omega$ /sq was prepared by physical vapor deposition (PVD) sputtering. 9 nm HfO<sub>2</sub> was deposited at 320 °C by the reaction of O<sub>2</sub> and tetrakis(ethylmethylamido)hafnium (Hf(NMeEt)<sub>4</sub>) onto TiN in an atomic vapor deposition (AVD) chamber. Finally, HfO<sub>2</sub> was capped by 7 nm ionized metal plasma (IMP) Ti and 150 nm PVD TiN [15]. To investigate the impact of inter-cell and intra-cell variability, 4 kbit RRAM arrays with 600 × 600 nm<sup>2</sup> MIM area and with 890 × 965 nm<sup>2</sup> 1T-1R area were processed [16]–[18]. Memory array characterization was performed for 20 packaged memory arrays on a dedicated automated Active Technologies RIFLE system [16].

### **III. RESULTS AND DISCUSSION**

### A. Inter-cell variability in initial state and after d.c. forming

In this section, we present the influence of the d.c. forming process on the inter-cell variability. Forming was a prerequisite to induce stable resistance changes in our devices. This process

TABLE I

Summary of DC forming, pulse-induced forming, pulse-retry forming, DC-retry forming, set/reset and read voltages.

|                       | Bitline (BL) voltage $V_{BL}$ | Sourceline (SL) voltage $V_{SL}$ | Wordline (WL) voltage $V_{WL}$ | Bitline (BL) pulse width $t_{BL, pulse}/Bitline$ (BL) sweep time |

|-----------------------|-------------------------------|----------------------------------|--------------------------------|------------------------------------------------------------------|

| d.c. forming          | 0 V - 2.3 V                   | 0 V                              | 1.4 V                          | 23 s                                                             |

| d.c. Set              | 0 V - 2.3 V                   | 0 V                              | 1.4 V                          | 23 s                                                             |

| d.c. Reset            | 0 V                           | 0 V - 2.3 V                      | 2.2 V                          | 23 s                                                             |

| Pulse-induced forming | 3.5 V                         | 0 V                              | 1.4 V                          | 10 µs                                                            |

| Pulse-retry forming   | 3.5 V                         | 0 V                              | 1.4 V                          | $10 \mu s$                                                       |

| d.c. retry forming    | 0 V - 3.5 V                   | 0 V                              | 1.4 V                          | -                                                                |

| Pulse set cycling     | 3 V                           | 0 V                              | 1.4 V                          | 10 µs                                                            |

| Pulse reset cycling   | 0 V                           | 3 V                              | 2.2 V                          | $10 \mu s$                                                       |

| Reading               | 0.3 V                         | 0 V                              | 1.4 V                          | -                                                                |

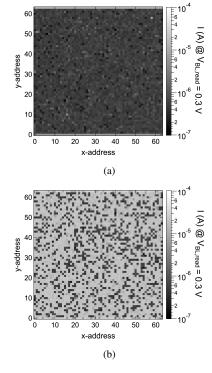

Fig. 1. Current distributions for a 64  $\times$  64 bit (4 kbit) RRAM array with 1T-1R devices with 600  $\times$  600 nm<sup>2</sup> MIM area. (a) Initial state. (b) After forming in d.c. step sweep. The gate-source voltage was set to V<sub>WL</sub> = 1.4 V with a bitline voltage sweep to V<sub>BL</sub> = 2.3 V with ramp rate dV/dt = 0.1 Vs<sup>-1</sup>. Current reading was performed at V<sub>WL</sub> = 1.4 V and V<sub>BL, read</sub> = 0.3 V.

consists in the application of a d.c. step sweep on the bitline (BL) to  $V_{BL} = 2.3$  V as well as grounding the sourceline (SL)  $V_{SL} = 0$  V. In contrast to d.c. voltage sweeps, current-driven d.c. step sweeps result in more reliable transitions into the bipolar switching mode in 1R devices by avoiding overshoot issues [19]. To prevent hard breakdown, the saturation current of the select transistor is controlled by the wordline (WL) voltage at  $V_{WL} = 1.4$  V. Table I summarizes the forming, set/reset and reading parameters in this work. In general, the forming process produces a non-destructive soft breakdown and progressive breakdown regime of the dielectric and requires a sufficiently high electric field across the HfO<sub>2</sub> film thickness [20], [22], [23]. Due to the stochastic nature of the forming process or due to process-induced variations, the inter-

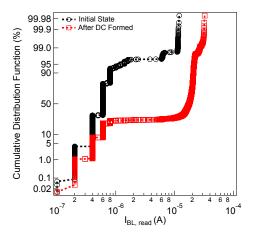

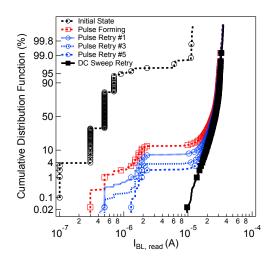

Fig. 2. Statistical current distributions of the initial state and after forming in d.c. step sweep. Current reading was performed at  $V_{WL} = 1.4 \text{ V}$  and  $V_{BL, read} = 0.3 \text{ V}$ .

cell variability of memory elements in a 4 kbit memory array cannot be neglected. To address this point, we first show in Fig. 1 the current distribution in the initial state which is defined by the combination of the Ti and  $HfO_2$  film thicknesses [18] and the current distribution after d.c. forming.

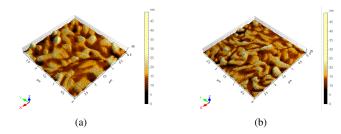

Statistical analysis in a cumulative distribution function plot in Fig. 2 reveals that only 78 % of the devices (red curve) were successfully formed by the d.c. step sweep, whereas 22% devices were not formed due to the high inter-cell variability of the initial state current. The thickness inhomogeneity of the PVD Ti layer with  $\sigma < 5\%$  standard deviation over the whole wafer diameter is believed not to play a central role in the intercell variability of the initial currents in Fig. 2 since the memory array with circuitry area is  $365 \times 752 \ \mu m^2$ . When compared with Ti, the thickness inhomogeneity of the HfO<sub>2</sub> film with  $\sigma < 2\%$  standard deviation should also be insignificant for the initial current inter-cell variability [24]. One reason could be the root mean square surface roughness of HfO<sub>2</sub> films due to the columnar structure of the TiN bottom metal electrode [25], although a post-metallization annealing (PMA) step was applied which was reported to reduce the surface roughness [26]. To support this hypothesis it is shown in Fig. 3 the different root mean square values of the roughness profiles extracted from TiN and HfO2 films used in RRAM arrays processing. The randomly distributed inter-cell variability after

Fig. 3. Roughness profile of the TiN (a) and  $HfO_2$  (b) films used in the array processing.

forming in d.c. step sweep is often related to intrinsic processes which involve microscopic transport of oxygen vacancies and permutations of filamentary clusters [9], [27], [28].

# *B.* Inter-cell variability in initial state and after pulse-induced forming

Recently, the pulse-induced forming has attracted wide attention as an alternative to d.c. forming. This pulse forming mode may reduce the operation current and the energy per unit volume imparted to the dielectric [29], [30]. Moreover, the forming time for the whole memory array can be reduced. To understand the pulse-induced forming process in more detail, we varied the forming parameters, namely V<sub>WL</sub>, V<sub>BL</sub>, and the voltage pulse width t<sub>BL, pulse</sub> on an adjacent memory array. For  $V_{WL} = 1.4 \text{ V}, V_{BL} = 3.5 \text{ V}, \text{ and } t_{BL, \text{ pulse}} = 10 \,\mu\text{s}, \text{ devices were}$ formed, which is comparable to d.c. forming (see Fig. 2). V<sub>WL</sub>,  $V_{BL}$  in conjunction with  $t_{BL, pulse}$  are critical parameters to initiate the pulse-induced forming process. Simplified analytical models reproduce the statistical distribution of the forming voltage  $V_{BL}$  for each device in the memory array [31], [32]. The pulse-induced forming energy density (voltage  $\times$  current  $\times$  time/area) imparted to the dielectric for each cell reaches an average value of  $1.9 \times 10^{-9} \text{ J}/\mu\text{m}^2$  in comparison to  $3.7 \times 10^{-3}$  $J/\mu m^2$  after d.c. forming.

From a physical point of view, the pulse-induced forming may be appreciated with the shape of the created conductive filament: while pulses with low  $V_{WL}$  and  $V_{BL}$  voltages or short pulse width  $t_{BL, pulse}$  create narrow filaments showing low currents, higher  $V_{WL}$  and  $V_{BL}$  voltages or long pulse width  $t_{BL, pulse}$  create stable and wider filaments [33]. The filament diameter and areal density may be correlated with the concentration of oxygen vacancies that are supposed to participate in the filament formation process. The oxygen vacancies are predominantly produced at the Ti metal electrode as the result of redox processes of the oxide by the Ti metal electrode [34]–[36].

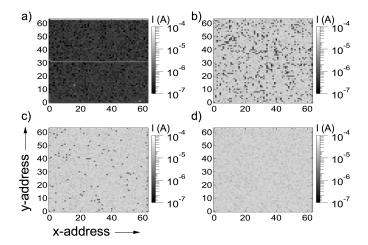

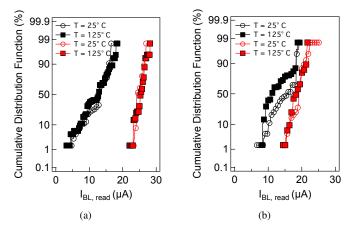

We applied thereafter these parameters to a fresh memory array. Figures 4(a) and 4(b) show the current distributions of the initial state and after pulse-induced forming. Statistical analysis in a cumulative distribution function plot in Fig. 5 reveals that 86 % of the devices were formed by the pulse process. A retry-algorithm was then implemented to form the remaining devices. The retry operations have been mostly required on cells with low initial currents. One reason could be that devices with a lower initial current need a higher energy density imparted to the dielectric to be formed. Forming with

Fig. 4. Current distributions for a 64  $\times$  64 bit (4 kbit) RRAM array with 1T-1R devices with 600  $\times$  600 nm<sup>2</sup> MIM area. (a) Initial state. (b) After pulse-induced forming. V<sub>WL</sub> was set to 1.4 V with V<sub>BL</sub> = 3.5 V and t<sub>BL, pulse</sub> = 10  $\mu$ s: total 86% formed. (c) After applying a retry-algorithm to unformed devices: total 97.6% formed. (d) After d.c. forming of the devices not formed by the retry step: total 100% formed. Current reading was performed at V<sub>WL</sub> = 1.4 V and V<sub>BL, read</sub> = 0.3 V.

Fig. 5. Statistical current distributions of the initial state, after pulse-induced forming and after application of retry-algorithms. Current reading was performed at  $V_{WL} = 1.4 \text{ V}$  and  $V_{BL, read} = 0.3 \text{ V}$ .

the same parameters as before was applied 5 times on BLs with unformed devices. This increased the fraction of formed devices in the array to 97.6% (Figs. 4(c) and 5). The remaining 2.4% devices could be formed by a d.c. forming step (Figs. 4(d) and 5). After forming, positive  $V_{SL}$  step sweeps with  $V_{WL}$  = 2.2 V and  $V_{BL}$  = 0 V reset the devices to the high resistance OFF state. Positive  $V_{BL}$  step sweeps with  $V_{WL}$ =1.4 V and  $V_{SL}$  = 0 V set the devices to the low resistance ON state (Table I). The OFF/ON resistance contrast on repeated switching cycles remains typically between 1.4 to 10.

### C. Intra-cell variability in set/reset endurance and after bake

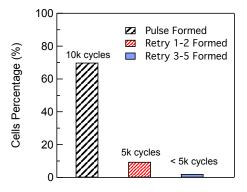

We performed set/reset pulse operations after pulse forming and after pulse-retry forming to evaluate the cycling endurance (Fig. 6). 70 % of the devices formed with the first forming

Fig. 6. Set/reset cycling endurance after pulse-induced forming and after pulse-retry forming.

pulse show the highest endurance, whereas almost 16% of them evidenced resistance switching issues after a possible over-forming process [40].

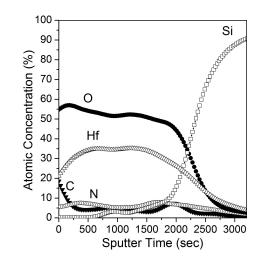

As the number of forming-retry pulses increases, the resistance switching capability of the conductive filament is strongly impacted: retry-formed cells show lower cycling endurance compared to single-pulse formed cells. The retrieved endurance of 10<sup>4</sup> cycles is significantly lower than what retrieved for similar arrays [33], [41] and this could be attributed to the impact of impurities in the metal-organic AVD precursor, in particular to carbon [36]. To support such a consideration, Fig. 7 shows a XPS depth profile measurement of a 50 nm thick HfO<sub>2</sub> deposited on a silicon substrate. Since the cells embedded into the array are too small for the analysis, XPS profile has been measured on cells with a higher HfO<sub>2</sub> stack, but processed with the same deposition parameters used for the MIM cells in the array. A high presence of carbon and nitrogen atoms can be observed: these impurities are caused by the liquid metal-organic precursor, used for the AVD deposition process. Their presence severely limits the oxide performance and wears the cells in the array faster than any other degradation mechanism.

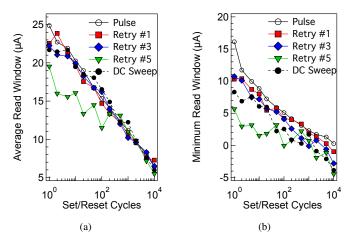

To evaluate the relationship between forming conditions and endurance, formed cells with a single pulse, after 1, 3, 5 forming-retry pulses and after d.c. step sweep were considered (Tab. I). Figures 8 (a) and 8 (b) show the average and minimum (i.e. considering the worst-case condition) read window calculated during cycling for each cell subset [16]. For all cell subsets both average and minimum read window decrease with increasing number of cycles.

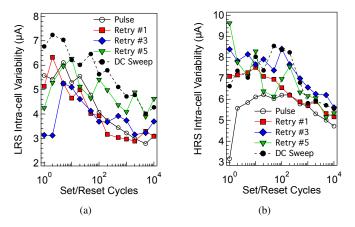

Figure 9 (a) shows the ON state (LRS) intra-cell variability during cycling, which indicates decrease for each cell subset. The highest variability is observed on cells formed after 5 pulse-retry algorithms and after d.c. step sweeps. Similar behavior is observed for the OFF state (HRS) intra-cell variability during cycling in Fig. 9 (b). The reduction of the intra-cell variability during cycling is given by the fact that a consecutive set/reset operation brings all cells toward a uniform wear-out condition of the conducting filament, therefore reducing the fluctuations due to structural modifications of the conduction path in the memory cells [11].

In order to investigate the reason underlying different

4

Fig. 7. XPS depth profile measurement of a 50 nm thick HfO<sub>2</sub> RRAM cell.

Fig. 8. (a) Average and (b) minimum read window after a single pulse, after 1, 3, 5 forming-retry pulses and after d.c. step sweep.

Fig. 9. Intra-cell variability during  $10^4$  pulse set/reset cycling for (a) LRS and (b) HRS.

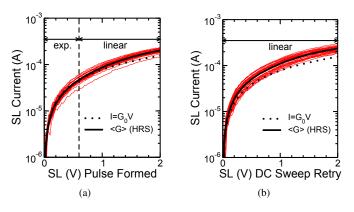

Fig. 10. HRS I-V curves measured on cycled devices after Reset on cells formed with a single pulse (a) and with DC retry operation (b).

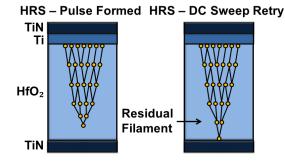

Fig. 11. Schematic showing the conductive filament shape after reset (HRS) for Pulse and DC Retry formed cells.

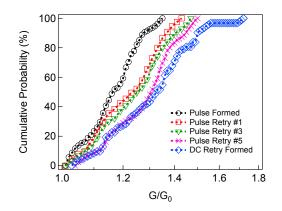

degradation speed for different forming retry times, I-V measurements of the Reset operation have been performed at endurance cycle  $10^4$ . Fig. 10 shows HRS I-V curves of the cells formed with a single pulse (a) or with DC sweep retry operations (b). The black dashed line shows the limit  $I = G_0 V$ with  $G_0 = 2e^2/h$  equal to the quantum conductance unit corresponding to the creation of a single mode nanowire according to Quantum Contact Point (QPC) model [20], where e is the electron charge and h the Planck's constant. The average < G > curves measured after Reset is shown for sake of comparison. Within this framework, in case of  $I > G_0 V$  the presence of a residual conductive filament has to be taken into account. Cells formed with a single pulse show lower average conductance values after Reset, even after cycling. Moreover, on single pulse formed cells an exponential ( $V_{SL} < 0.6V$ ) plus linear ( $V_{SL} > 0.6V$ ) current behavior can be observed since  $\langle G \rangle$  is very close to  $I = G_0 V$  limit, whereas only linear behavior is observed on  $\langle G \rangle$  of DC sweep retry formed cells. This indicates that for single pulse formed cells, the filament geometry after cycling in reset condition still evidences a potential barrier giving rise to direct tunneling transport through a material barrier or through a residual confinement barrier (QPC) [30] (i.e., the exponential part of the curve), whereas for DC sweep retry formed cells only the ohmic component is present due to worn-out filament (see Fig. 11). Fig. 12 shows the cumulative distribution of conductance values measured after Reset operation of cells formed at different retry steps: cells formed with a higher number of retry operations show higher conductance values and intra-

Fig. 12. Cumulative distribution of conductance values measured after Reset on cycled cells.

cell variability. More retry steps allow the cells to reach a more stable state resulting in higher conductance values yet displaying lower switching capabilities. More energy is indeed required in these cells in order to create the conductive filament compared to single pulse formed cells, hence it can be expected that even during cycling a higher set/reset energy was required to create/disrupt the filament on such cells. Due to such lack of energy, a higher intra-cell variability is observed since set/reset operations were not correctly performed on all retry-formed cells.

Figure 13 shows the cumulative distribution function plots for the first (a) and for the  $10^4$  (b) cycle for pulsed set/reset operations. A 24-hour temperature bake at  $125 \,^{\circ}$ C has been applied before and after set/reset cycling on different arrays. The LRS and HRS average currents do not show any relevant variation after bake for both fresh and cycled devices (Tab.II).

Fig. 13. Statistical current distributions of the temperature bake at cycle (a) 1 and after (b)  $10^4$  set/reset cycles for the LRS state (red curves) and for the HRS state (black curves) obtained with the following set/reset pulse conditions:  $V_{BL/SL} = 3 V$  and  $t_{BL, pulse} = 10 \ \mu s$  (Tab. I).

## IV. CONCLUSION

This paper has presented results on the inter-cell variability of the initial state and the impact of d.c. and pulse forming on inter-cell as well as on intra-cell variability in 4 kbit memory arrays. 100 % of devices in a memory array must be formed

TABLE II HRS/LRS statistics before and after a 24 hours temperature bake at 125  $^{\circ}\mathrm{C}.$

|              | Cycle 1          |                  | Cycle 10 <sup>4</sup> |                  |

|--------------|------------------|------------------|-----------------------|------------------|

|              | $\mu$ ( $\mu$ A) | $\sigma~(\mu A)$ | $\mu$ ( $\mu$ A)      | $\sigma~(\mu A)$ |

| HRS (25 °C)  | 11.9             | 3.7              | 13.1                  | 3.0              |

| HRS (125 °C) | 11.8             | 3.7              | 12.1                  | 4.1              |

| LRS (25 °C)  | 25.2             | 1.1              | 18.5                  | 2.7              |

| LRS (125 °C) | 25.3             | 1.3              | 18.5                  | 1.8              |

to guarantee a product maturity level for RRAM, however, we observe that on particular arrays only 78 % are d.c. formed. The insights suggest a combination of the extrinsic process-induced variability of the initial state and intrinsic variability after forming as origin. Pulse-induced forming was achieved by choosing 10  $\mu$ s pulses as well as by V<sub>BL</sub> = 3.5 V and  $V_{WL} = 1.4$  V. These parameters were applied to the memory array. Using a retry algorithm, we achieve 100 % of pulse-formed devices. However, the endurance of retry-formed devices decreased faster compared to pulse-formed devices with a single pulse. One possible physical explanation for the endurance degradation could be impurities in the metal-organic AVD precursor. The fitting of the I-V curves after different pulse forming steps by using the QPC model offers a route to the understanding of the degradation process within a physical framework.

### ACKNOWLEDGMENT

We thank the Off-Line characterization and Pilot-Line group at IHP for memory array processing. The authors particularly wish to thank T. Kerekes from NplusT Semiconductor Application Center. This work was financially supported by the German research foundation DFG under contract SCHR1123/7-1 and by ENIAC Joint Undertaking 2013-2, PANACHE No. 621217.

### REFERENCES

- J. Suhonen, M. Kohvakka, V. Kaseva, T. D. Hämäläinen, and M. Hännikäinen, Low-Power Wireless Sensor Networks: Protocols, Services and Applications, Springer, 2012.

- [2] B. de Salvo, Silicon Non-Volatile Memories: Paths of Innovation, Hoboken, Wiley-ISTE, 2009.

- [3] Y. Zhang, Future Wireless Networks and Information Systems, Springer, 2012.

- [4] Y. S. Chen, H. Y. Lee, P. S. Chen, P. Y. Gu, C. W. Chen, W. P. Lin, W. H. Liu, Y. Y. Hsu, S. S. Sheu, P. C. Chiang, W. S. Chen, F. T. Chen, C. H. Lien, and M.-J. Tsai, "Highly Scalable Hafnium Oxide Memory with Improvements of Resistive Distribution and Read Disturb Immunity," *IEDM*, pp. 105-108, 2009.

- [5] H. Y. Lee, Y. S. Chen, P. S. Chen, P. Y. Gu, Y. Y. Hsu, S. M. Wang, W. H. Liu, C. H. Tsai, S. S. Sheu, P. C. Chiang, W. P. Lin, C. H. Lin, W. S. Chen, F. T. Chen, C. H. Lien, and M.-J. Tsai, "Evidence and solution of Over-RESET Problem for HfOx Based Resistive Memory with Sub-ns Switching Speed and High Endurance," *IEDM*, pp. 460-463, 2010.

- [6] S.-S. Sheu, M.-F. Chang, K.-F. Lin, C.-W. Wu, Y.-S. Chen, P.-F. Chiu, C.-C. Kuo, Y.-S. Yang, P.-C. Chiang, W.-P. Lin, C.-H. Lin, H.-Y. Lee, P.-Y. Gu, S.-M. Wang, F. T. Chen, K.-L. Su, C.-H. Lien, K.-H. Cheng, H.-T. Wu, T.-K. Ku, M.-J. Kao, and M.-J. Tsai, "A 4 Mb embedded SLC resistive-RAM macro with 7.2 ns read-write random-access time and 160 ns MLC-access capability," *Proc. ISSCC*, pp. 200-202, Feb. 2011.

- [7] T.-Y. Liu, T. H. Yan, R. Scheuerlein, Y. Chen, J. K. Lee, G. Balakrishnan, G. Yee, H. Zhang, A. Yap, J. Ouyang, T. Sasaki, S. Addepalli, A. Al-Shamma, C.-Y. Chen, M. Gupta, G. Hilton, S. Joshi, A. Kathuria, V. Lai, D. Masiwal, M. Matsumoto, A. Nigam, A. Pai, J. Pakhale, C. H. Siau, X. Wu, R. Yin, L. Peng, J. Y. Kang, S. Huynh, H. Wang, N. Nagel, Y. Tanaka, M. Higashitani, T. Minvielle, C. Gorla, T. Tsukamoto, T. Yamaguchi, M. Okajima, T. Okamura, S. Takase, T. Hara, H. Inoue, L. Fasoli, M. Mofdi, R. Shrivastava, and K. Quader, "A 130.7 mm<sup>2</sup> 2-Layer 32 Gb ReRAM Memory Device in 24 nm Technology," *Proc. ISSCC*, pp. 210-212, Feb. 2013.

- [8] G. W. Burr, M. J. Breitwisch, M. Franceschini, D. Garetto, K. Gopalakrishnan, B. Jackson, B. Kurdi, C. Lam, L. A. Lastras, A. Padilla, B. Rajendran, S. Raoux, and R. S. Shenoy, "Phase change memory technology," *J. Vac. Sci. Technol. B*, vol. 28(2), pp. 223-262, 2010.

- [9] N. Raghavan, R. Degraeve, A. Fantini, L. Goux, D. J. Wouters, G. Groeseneken, and M. Jurczak, "Stochastic Variability of Vacancy Filament Configuration in Ultra-Thin Dielectric RRAM and its Impact on OFF-State Reliability," *IEDM*, pp. 554-557, 2013.

- [10] S. Long, X. Lian, T. Ye, C. Cagli, L. Perniola, E. Miranda, M. Liu, J. Suñé, "Cycle-to-Cycle Intrinsic RESET Statistics in HfO<sub>2</sub>-Based Unipolar RRAM Devices," *IEEE Electron Device Lett.*, vol. 34, no. 5, pp. 623-625, May 2013.

- [11] K. Higuchi, T. O. Iwasaki, and K. Takeuchi, "Investigation of Verify-Programming Methods to Achieve 10 Million Cycles for 50 nm HfO<sub>2</sub> ReRAM," 4th IEEE International Memory Workshop (IMW), pp. 1-4, 2012.

- [12] S. Yu, G. Ximeng, and H.-S. P. Wong, "On the Switching Parameter Variation of Metal Oxide RRAM Part II: Model Corroboration and Device Design Strategy," *IEEE Trans. Electron Devices*, vol. 59, no. 4, pp. 1183-1188, Apr. 2012.

- [13] A. Benoist, S. Blonkowski, S. Jeannot, S. Denorme, J. Damiens, J. Berger, and P. Candelier, "28 nm Advanced CMOS Resistive RAM Solution as Embedded Non-Volatile Memory," *IEEE International Reliability Physics Symposium (IRPS)*, pp. 2E.6.1-2E.6.5, Jun. 2014.

- [14] A. Chen and M.-R. Lin, "Variability of resistive switching memories and its impact on crossbar array performance," *IEEE International Reliability Physics Symposium (IRPS)*, pp. MY.7.1-MY.7.4, Apr. 2011.

- [15] Ch. Walczyk, D. Walczyk, Th. Schroeder, Th. Bertaud, M. Sowinska, M. Lukosius, M. Fraschke, D. Wolansky, B. Tillack, E. Miranda, and C. Wenger, "Impact of Temperature on the Resistive Switching Behavior of Embedded HfO<sub>2</sub>-Based RRAM Devices," *IEEE Trans. Electron Devices*, vol. 58, no. 9, pp. 3124-3131, Sep. 2011.

- [16] C. Zambelli, A. Grossi, P. Olivo, D. Walczyk, J. Dabrowski, B. Tillack, T. Schroeder, V. Stikanov, and C. Walczyk, "Electrical characterization of read window in ReRAM arrays under different SET/RESET cycling conditions," *IEEE International Memory Workshop (IMW)*, pp. 1-4, 2014.

- [17] C. Zambelli, A. Grossi, D. Walczyk, T. Bertaud, B. Tillack, T. Schroeder, V. Stikanov, P. Olivo, and C. Walczyk, "Statistical analysis of resistive switching characteristics in ReRAM test arrays," in *IEEE International Conference on Microelectronics Test Structures (ICMTS)*, pp. 27-31, 2014.

- [18] D. Walczyk, T. Bertaud, M. Sowinska, M. Lukosius, M. A. Schubert, A. Fox, D. Wolansky, A. Scheit, M. Fraschke, G. Schoof, C. Wolf, R. Kraemer, B. Tillack, R. Korolevych, V. Stikanov, C. Wenger, T. Schroeder, and C. Walczyk, "Resistive switching behavior in TiN/HfO<sub>2</sub>/Ti/TiN devices," *Proc. ISCDG*, pp. 143-146, Sept. 2012.

- [19] D. S. Jeong, R. Thomas, R. S. Katiyar, J. F. Scott, H. Kohlstedt, A. Petraru, and C. S. Hwang, "Emerging memories: resistive switching mechanisms and current status," *Rep. Prog. Phys.*, vol. 75, 076502, pp. 1-31, 2012.

- [20] E.A. Miranda, Ch. Walczyk, C. Wenger, and Th. Schroeder, "Model for the Resistive Switching Effect in HfO<sub>2</sub> MIM Structures Based on the Transmission Properties of Narrow Constrictions," *IEEE Electron Device Lett.*, vol. 31, no. 6, pp. 609-611, 2010.

- [21] Y. Y. Chen, R. Degraeve, S. Clima, B. Govoreanu, L. Goux, A. Fantini, G. S. Kar, G. Pourtois, G. Groeseneken, D. J. Wouters, and M. Jurczak, "Understanding of the endurance failure in scaled HfO<sub>2</sub>-based 1T1R RRAM through vacancy mobility degradation," *IEDM*, pp. 482-485, 2012.

- [22] S. Karg, G. Meijer, J. Bednorz, C. Rettner, A. Schrott, E. Joseph, C. Lam, M. Janousch, U. Staub, F. L. Mattina, S. Alvarado, D. Widmer, R. Stutz, U. Drechsler, and D. Caimi, "Transition-metal-oxide-based resistancechange memories," IBM Journal of Research and Development, vol. 52, no. 4.5, pp. 481-492, 2008.

- [23] N. Raghavan, A. Fantini, R. Degraeve, P. J. Roussel, L. Goux, B. Govoreanu, D. J. Wouters, G. Groeseneken and M. Jurczak, "Statistical insight into controlled forming and forming-free stacks for HfOx RRAM," *Microelectron. Eng.*, vol. 109, pp. 177-181, Sep. 2013.

- [24] G. Jegert, A. Kersch, W. Weinreich, and P. Lugli, "Ultimate scaling of TiN/ZrO<sub>2</sub>/TiN capacitors: Leakage currents and limitations due to electrode roughness," J. Appl. Phys., 109, 014504, 2011.

- [25] P.-S. Chen, Y.-S. Chen, H.-Y. Lee, T.-Y. Wu, P.-Y. Gu, F. Chen, and M.-J. Tsai, "Impact of Flattened TiN Electrode on the Memory Performance of HfO<sub>2</sub> Based Resistive Memory," Electrochem. Solid-State Lett., 15 (4) H136-H139, 2012.

- [26] J. Mueller, A. Singh, S. Riedel, J. Sundqvist, U. Schroeder, and T. Mikolajick, "Incipient Ferroelectricity in Al-Doped HfO<sub>2</sub> Thin Films," Adv. Funct. Mater., 22, 2412-2417, 2012.

- [27] S.E. Savelev, A.S. Alexandrov, A.M. Bratkovsky, and R. Stanley Williams, "Molecular dynamics simulations of oxide memristors: thermal effects," *Appl Phys A.*, vol. 102, pp. 891-895, 2011.

- [28] L. Larcher, O. Pirrotta, F. M. Puglisi, A. Padovani, P. Pavan, and L. Vandelli, "Progresses in modeling HfOx RRAM operations and variability," *ECS Transactions*, vol. 64 (14), pp. 49-60, 2014.

- [29] F. T. Chen, H. Y. Lee, Y. S. Chen, Y. Y. Hsu, L. J. Zhang, P. S. Chen, W. S. Chen, P. Y. Gu, W. H. Liu, S. M. Wang, C. H. Tsai, S. S. Sheu, M. J. Tsai, and R. Huang, "Resistance switching for RRAM applications," *Sci. China Inf. Sci.*, vol. 54, no. 5, pp. 1073-1086, May 2011.

- [30] T.-J. Chu, T.-C. Chang, T.-M. Tsai, H.-H. Wu, J.-H. Chen, K.-C. Chang, T.-F. Young, K.-H. Chen, Y.-E. Syu, G.-W. Chang, Y.-F. Chang, M.-C. Chen, J.-H. Lou, J.-H. Pan, J.-Y. Chen, Y.-H. Tai, C. Ye, H. Wang, and S. M. Sze, "Charge Quantity Influence on Resistance Switching Characteristic During Forming Process," *IEEE Electron Device Lett.*, vol. 34, no. 4, pp. 502-504, Apr. 2013.

- [31] L. Vandelli, A. Padovani, L. Larcher, and G. Bersuker, "Microscopic Modeling of Electrical Stress-Induced Breakdown in Poly-Crystalline Hafnium Oxide Dielectrics," *IEEE Trans. Electron Devices*, vol. 60, no. 5, pp. 1754-1762, May 2013.

- [32] A. Chen, "Area and Thickness Scaling of Forming Voltage of Resistive Switching Memories," *IEEE Electron Device Lett.*, vol. 35, no. 1, pp. 57-59, Jan. 2014.

- [33] Y. Y. Chen, B. Govoreanu, L. Goux, R. Degraeve, A. Fantini, G. S. Kar, D. J. Wouters, G. Groeseneken, J. A. Kittl, M. Jurczak, and L. Altimime, "Balancing SET/RESET Pulse for > 10<sup>10</sup> Endurance in HfO<sub>2</sub>/Hf 1T1R Bipolar RRAM," IEEE Trans. Electron Devices, vol. 59, no. 12, pp. 3243-3249, 2012.

- [34] T. Bertaud, M. Sowinska, D. Walczyk, S. Thiess, A. Gloskovskii, Ch. Walczyk, and T. Schroeder, Appl. Phys. Lett., 101, 143501, 2012.

- [35] P. Calka, M. Sowinska, T. Bertaud, D. Walczyk, J. Dabrowski, P. Zaumseil, Ch. Walczyk, A. Gloskovskii, X. Cartoixa, J. Suñé, and T. Schroeder, ACS Appl. Mater. Interfaces, 6 (7), pp. 5056-5060, 2014.

- [36] M. Sowinska, T. Bertaud, D. Walczyk, S. Thiess, P. Calka, L. Alff, Ch. Walczyk, and T. Schroeder, J. Appl. Phys., 115, 204509, 2014.

- [37] Z. Fang, X. P. Wang, X. Li, Z. X. Chen, A. Kamath, G. Q. Lo, and D. L. Kwong, "Fully CMOS-Compatible 1T1R Integration of Vertical Nanopillar GAA Transistor and Oxide-Based RRAM Cell for High-Density Nonvolatile Memory Applications," *IEEE Trans. Electron Devices*, vol. 60, no. 3, pp. 1108-1113, Mar. 2013.

- [38] T.-W. Kim, H. Choi, S.-H. Oh, G. Wang, D.-Y. Kim, H. Hwang, and T. Lee, "One Transistor-One Resistor Devices for Polymer Non-Volatile Memory Applications," *Adv. Mater.*, vol. 21, pp. 2497-2500, 2009.

[39] E. Miranda, D. Jiménez and J. Suñé, "The quantum point-contact

- [39] E. Miranda, D. Jiménez and J. Suñé, "The quantum point-contact memristor," *IEEE Electron Device Lett.*, vol. 33, no.10, pp. 1474-1476, Oct. 2012.

- [40] H.-C. Shih, C.-Y- Chen, C.-W. Wu, C.-H. Lin, and S.-S. Sheu, "Training-Based Forming Process for RRAM Yield Improvement," *IEEE Test Symposium*, pp. 146-151, 2011.

- [41] P. Huang, B. Chen, Y. J. Wang, F. F. Zhang, L. Shen, R. Liu, L. Zeng, G. Du, X. Zhang, B. Gao, J. F. Kang, X. Y. Liu, X. P. Wang, B. B. Weng, Y. Z. Tang, G.-Q. Lo, and D.-L. Kwong, "Analytical Model of Endurance Degradation and Its Practical Applications for Operation Scheme Optimization in Metal Oxide Based RRAM," *IEDM*, pp. 597-600, 2013.

Alessandro Grossi received the M.Sc. degree in electronic and telecommunications engineering from the University of Ferrara, Ferrara, Italy, in 2013. He is currently pursuing the Ph.D. degree in Engineering Science within the Department of Engineering, University of Ferrara. He is currently working on the electrical characterization and modeling of emerging non-volatile memories.

**Damian Walczyk** (S'06–M'10) received a Dipl.-Ing. (FH) degree in microsystems engineering from the University of Applied Sciences in Münster, Münster, Germany, in 2009, and the M.Sc. degree in electrical and computer engineering from the University of Hagen, Hagen, Germany, in 2015. He joined IHP, Frankfurt (Oder), Germany, in 2010, and since then, he has been working on the electrical characterization of HfO<sub>2</sub>-based RRAM devices.

**Cristian Zambelli** (S'08–M'13) received the M.Sc. and Ph.D. (Hons.) degrees in electronic engineering from the University of Ferrara, Ferrara, Italy, in 2008 and 2012, respectively. He has held an Assistant Professor position with the Department of Engineering, University of Ferrara, since 2015. His current research interests include the characterization, physics, and modeling of nonvolatile memories reliability.

**Enrique Miranda** (SM'10) received the Ph.D. degree in electronics enginnering with the Universitat Autónoma de Barcelona (UAB), Spain, in 1999 and the Ph.D. degree in physics with the Universidad de Buenos Aires, Argentina, in 2001. Since 2006, he has been Professor with the Escola d'Enginyeria, UAB. His research interests are conduction mechanisms in dielectric films, oxide reliability, memristive and resistive switching devices.

**Piero Olivo** received the Ph.D. degree in electronic engineering from the University of Bologna, Bologna, Italy, in 1987. He has been a Full Professor of Electronics with the University of Ferrara, Ferrara, Italy, since 1994. His current research interests include the theoretical and experimental aspects of microelectronics, with an emphasis on physics, reliability, and characterization of electron devices and nonvolatile memories.

Valeriy Stikanov graduated from Kiev Polytechnic Institute, Faculty of Electronics, Department of Microelectronics, Kiev, Ukraine, in 1971. In 1987 he received the Ph.D. degree in microelectronic engineering. Since 1996 he is Professor of the System Analysis Department at the Kiev Polytechnic Institute. His scientific activity concerns the writing, erasing, degradation and storage of charge in nonvolatile memory devices.

**Bernd Tillack** received a Ph.D. degree from Halle-Merseburg University, Merseburg, Germany, in 1980. His research interests include SiGe BiC-MOS technology development following the "More than Moore" strategy for embedded system applications. He is also currently with the Berlin Institute of Technology (TU Berlin), Berlin, Germany, as a Professor for Si-based high-frequency technologies.

Alessandro Feriani graduated in Electronic Engineering from Perugia University, Perugia, Italy, in 2002. Since 2005, he is working for NplusT Semiconductor Application Center, Perugia, Italy, and he is responsible for application, memory tester and software engineer duties.

Alexander Fox received a Diploma degree in electrical engineering from the RWTH Technical University Aachen, Germany, in 1999, and a Ph.D. degree from the Christian-Albrechts-Universität Kiel, Germany, in 2006. In 2000, he joined IHP in Frankfurt (Oder), Germany, where he has been working on integration issues of a  $0.25\mu$ m BiCMOS technology, Embedded Flash memory module into a SiGe:C BiCMOS baseline technology, and on SiGe bipolar transistors.

**Jordi Suñé** graduated in Physics in 1986 and received a Ph.D. degree in Electronics in 1989 both at the Universitat Autònoma de Barcelona (UAB), Bellaterra, Spain. He is Fellow of the IEEE for contributions to the understanding of gate oxide failure and reliability methodology. He has (co-)authored more than 150 papers in international journals and relevant conferences. His main fields of interest are gate oxide physics and reliability, resistive switching devices and oxide-based electronics.

Thomas Schroeder received a diploma in Chemistry in 1996 and a diploma in Physics in 1998 from the University of Tübingen. He passed his Ph.D. research at the Fritz-Haber Institute in Berlin and joined IHP in 2004. Prof. Schroeder is the Department Head of IHP's Materials Research Department and he is Professor in Physics at the TU Brandenburg-Senftenberg in Cottbus, Germany. He has authored and co-authored about 160 papers in peer-reviewed journals and he holds about 15 patents in Si microelectronics.

**Gunter Schoof** received his Diploma degree in information technology from the Technische Universität Chemnitz, Germany, in 1983. Since 2003, he is working in the System Design Department at IHP, Frankfurt (Oder), Germany. He is responsible for the implementation and test of new IP components in a digital design library and investigates new methods and concepts of digital ASIC designs using faulttolerant design techniques.

**Christian Wenger** received a Diploma degree in physics from the University of Konstanz, in 1995 and a Ph.D. degree from the Technical University of Dresden, in 2000. Since 2002, he has been with IHP where he is working in the field of BEOL functional devices. In 2009, he received a post-doctoral degree at TU Dresden. He has authored and co-authored more than 100 papers and holds 6 patents.

**Rolf Kraemer** received his Diploma degree and a Ph.D. degree from RWTH Aachen in Electrical Engineering and Computer Science in 1979 and 1985. He joined the Philips Research Laboratories in 1985 where he worked on distributed operating systems and wireless high speed communication in Hamburg and Aachen until 1998. In 1998, he became Professor at the Technical University of Cottbus with the joined appointment of the Department Head in System Design at IHP, Frankfurt (Oder), Germany.

**Christian Walczyk** received a M.Sc. degree in Electrical Engineering from the University of Siegen, Germany, in 2007. Since 2007, he is with with the Materials Research Department at IHP, Frankfurt (Oder), Germany. He finished his Dr.-Ing. degree in Electrical Engineering at Technische Universität Berlin, Germany, in 2011. He has (co)authored 30 publications in peer-reviewed journals.