Das Joint Lab Wireless and Embedded System Design wurde 2015 zusammen mit dem Institut für Informatik der Universität Potsdam gegründet. Um Synergien zu schaffen, unterhält das IHP am Campus Griebnitzsee zusammen mit dem Fachbereich Informatik direkt neben dem Fachbereich Informatik Büros und ein Hardwarelabor. Das Hardwarelabor wird von Studenten, Mitarbeitenden des IHP und des Fachbereichs Informatik für Lehre und Forschung genutzt. Das Labor wird insbesondere von Studierenden genutzt, die in gemeinsamen Projekten arbeiten.

-

Forschung >> hier klicken <<

Der Forschungsschwerpunkt des Joint Labs ist die Entwicklung von:

- Middleware-Plattformen, energiesparenden Architekturen und zuverlässigen Kommunikationstechniken für drahtlose Kommunikationssysteme und Sensornetzwerke mit dem Fokus auf Assisted Living-, Industrie 4.0-, Automotive-, Avionic-, Telematik- und Telemedizinanwendungen

- verteilten und geclusterten Systeme für unterschiedlich starke Anforderungen hinsichtlich Zuverlässigkeit und Sicherheit

- Entwurfs- und Testmethoden für zuverlässige, sichere und fehlertolerante eingebettete Systeme und SoCs

- Low-Power- und Low-Noise-SoC-Entwurfsmethoden für innovative Schaltkreistechnologien, wie beispielsweise GALS, asynchrone und differentielle Logik

Die Kompetenzen des IHP und des Instituts für Informatik und Computational Science werden in dem Joint Lab in vier wichtigen Forschungsbereichen gebündelt:

- drahtlose Systeme und Sensornetze

- parallele Systeme und eingebetteter SoC-Entwurf

- Anwendungen für das Internet der Dinge und Service Multimedia

- Zuverlässigkeit, Sicherheit, Compliance

-

Projekte >> hier klicken <<

ENROL (DFG)

-

Publikationen >> hier klicken <<

Patente

- M. Krstic, G. Schoof, V. Petrovic, S. Weidling, E. Sogomonyan, M. Gössel, Schaltungsanordnung mit Detektion oder Behandlung von transienten Fehlern in einem kombinatorischen Schaltungsteil, Deutsche Patentanmeldung 102013225039.B4, Mai 2016.

- M. Augustin, M. Gössel, R. Kraemer, Elektronische Schaltungsanordnung zum Verarbeiten von binären Eingabewerten (Fehlertolerante Schaltungsarchitektur mit reduziertem Flächenaufwand), DE-Patentanmeldung am 29.01.2010, AZ: DE 10 2010 006 383.5.

Journalbeiträge

- F. Kuentzer, M. Krstic, Soft Error Detection and Correction Architecture for Asynchronous Bundled Data Designs, IEEE Transactions on Circuits and Systems I: Regular Papers, Digital Object Identifier: 10.1109/TCSI.2020.299891,early access.

- M. Dug, St. Weidling, E. Sogomonyan, D. Jokic, M. Krstic, Full Error Detection and Correction Method Applied on Pipelined Structure Using Two Approaches, Journal of Circuits, Systems, and Computers (JCSC), 2020

- F.A. Kuentzer, L. Juracy, M. Moreira, A. Amory, Testing the Blade Resilient Asynchronous Template,Analog Integrated Circuits and Signal Processing (2020)

- F. Mühlbauer, L. Schröder, M. Schölzel, Handling of Transient and Permanent Faults in Dynamically Scheduled Super-Scalar Processors, Microelectronics Reliability 80, 176 (2018)

- M. Krstic, S. Weidling, V. Petrovic, E. Sogomonyan, Enhanced Architectures for Soft Error Detection and Correction in Combinational and Sequential Circuits, Microelectronics Reliability, Volume 56, Januar 2016, Seiten 212–220, DOI: doi:10.1016/j.microrel.2015.10.022.

Konferenzbeiträge

- F. Kuentzer, M. Herrera, O. Schrape, P. Beerel, M. Krstic, Radiation Hardened Click Controllers for Soft Error Resilient Asynchronous Architectures, 26th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC) 2020

- F.A. Kuentzer, L.R. Juracy, M.T. Moreira, A.M. Amory, Test Oriented Design and Layout Generation of an Asynchronous Controller for the Blade Template, Proc. 26th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC 2020), 86 (2020)

- F. Kuentzer, M. Krstic, Soft error detection and correction architecture for asynchronous bundled data designs, 25th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC) 2019, Fresh Ideas Workshop

- F.A. Kuentzer, L.R. Juracy, M.T. Moreira, A.M. Amory, Delay Lines Test Method for the Blade Template, Proc. 25th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC 2019), (2019)

- L. Schröder, F. Mühlbauer, M. Schölzel Kombination von on-line und off-line Fehlerbehandlung in dynamisch geplanten Prozessoren, Proc. 30. GI/GMM/ITG-Workshop Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2018), 36 (2018)

- F. Mühlbauer, L. Schröder, M. Schölzel, A Fault Tolerant Dynamically Scheduled Processor with Partial Permanent Fault Handling, Proc. 19th IEEE Latin-American Test Symposium (LATS 2018), (2018)

- F. Meinel, N. Kluge, R. Wollowski, Improving Transistor Sizing for Asynchronous Circuits, Proc. 24th IEEE International Symposium on Asynchronous Circuits and Systems (ASYNC 2018), 1 (2018)

- M. Frohberg, S. Reinhold, P. Poppe, M. Schölzel, Test-Framework zur softwarebasierten Fehlerinjektion, -stimulation und Protokollierung von WSN-Anwendungen, Proc. 17. GI/ITG KuVS Fachgespräch Sensornetze (FGSN 2018), 39 (2018)

- N. Kluge, R. Wollowski, Data Path Optimisation and Delay Matching for Asynchronous Bundled-Data Balsa Circuits, 2017 International Conference On Computer Aided Design (ICCAD).

- F. Mühlbauer, M. Schölzel, Correcting Transient Faults Using Rollback with Low Overhead for Microcontrollers, Proc. International Workshop on Resiliency in Embedded Electronic Systems (REES 2017), 25 (2017)

- F. Mühlbauer, L. Schröder, P. Skoncej, M. Schölzel, Handling Manufacturing and Aging Faults with Software-based Techniques in Tiny Embedded Systems, Proc. IEEE Latin American Test Symposium (LATS 2017), (2017)

- F. Mühlbauer, M. Schölzel, Korrektur transienter Fehler durch Rollback mit geringem Software-Overhead für Mikrocontroller, Proc. Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2017), 53 (2017)

- F. Mühlbauer, L. Schröder, M. Schölzel, On Hardware-based Fault-Handling in Dynamically Scheduled Processors, Proc. IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS 2017), (2017)

- S. Weidling, M. Krstic, M. Gössel, Identifizierung fehlerbewahrender Speicherelemente zur Vermeidung der Fehlerakkumulation, ITG/GI/GMM-Workshop Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2017), Lübeck, March 05 - 07, 2017, Germany

- P. Skoncej, F. Mühlbauer, F. Kubicek, L. Schröder, M. Schölzel, Feasibility of Software-based Repair for Program Memories, Proc. 22nd IEEE International Symposium on On-Line Testing and Robust System Design (IOLTS 2016), 199 (2016)

- S. Weidling, M. Krstic, V. Petrovic, E. Sogomonyan, Architektur mit reduzierter Komplexität zur Erkennung und Korrektur von transienten Fehlern in kombinatorischer und sequentieller Logik, Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2016), Siegen, March 06 - 08, 2016, Germany.

- F. Mühlbauer, P. Skoncej, M. Schölzel, Softwarebasierte Fehlertoleranz für Flash-Speicher von mikrocontroller-basierten Systemen, Proc. ITG/GI/GMM-Workshop Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2016), (2016)

- F. Mühlbauer, M. Schölzel, Erkennung und Korrektur transienter Fehler durch Roll-back mit geringem Overhead, Proc. Dresdner Arbeitstagung Schaltungs- und Systementwurf (DASS 2016), 41 (2016)

- M. Frohberg, P. Poppe, N. Vetter, S. Reinhold, M. Schölzel, Cross-Plattform zur Hardware- und Betriebssystemunabhängigen Implementierung von Anwendungen und Protokollen, Proc. GI/ITG KuVS Fachgespräch Sensornetze (FGSN 2016), 47 (2016)

- S. Weidling, M. Krstic, V. Petrovic, M. Gössel, Neue Methodik zur Implementierung fehlertoleranter pipeline-basierter Architekturen, 27. Gesellschaft für Informatik / VDE/VDI-Gesellschaft Mikroelektronik, Mikrosystem- und Feinwerktechnik / Informationstechnische Gesellschaft im VDE – Workshop, Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ 2015).

- P. Skoncej, F. Mühlbauer, M. Schölzel, „Softwarebasierte Fehlertoleranz für Flash-Speicher von mikrocontroller-basierten Systemen“, FEES-Workshop 2015

- S. Taube, V. Petrovic, M. Krstic, Fault Tolerant Implementation of a SpaceWire Interface, 21st IEEE International Conference on Electronics Circuits and Systems (ICECS), December 7-10, 2014 Marseille, France.

- M. Krstic, S. Weidling, V. Petrovic, M. Gössel, Improved Circuitry for Soft Error Correction in Combinational Logic in Pipelined Designs, IEEE International On-Line Testing Symposium 2014.

- S. Zeidler, M. Goderbauer, M. Krstic, Design of a Low-Power Asynchronous Elliptic Curve Cryptography Coprocessor, IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Abu Dhabi, UAE, Dec, 2013.

- M. Augustin, M. Gössel, R. Kraemer, Entwurf fehlertoleranter Zustandsautomaten mit variablem Schutz für spezifische Eingabesequenzen, Proc. 24. GI/GMM/ITG-Workshop: Testmethoden und Zuverlässigkeit von Schaltungen und Systemen, 47 (2012)

- M. Augustin, M. Gössel, R. Kraemer, Effiziente Synthese von Schaltungen mit spezifischer Fehlertoleranz, Proc. 23. GI/GMM/ITG Workshop Testmethoden und Zuverlässigkeit von Schaltungen und Systemen (TuZ), 93 (2011)

- M. Augustin, M. Gössel, R. Kraemer , Implementation of Selective Fault Tolerance with Convential Synthesis Tools, Proc. 14th IEEE International Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS 2011), 213 (2011)

- M. Augustin, M. Gössel, R. Kraemer , Selective Fault Tolerance for Finite State Machines, Proc. 17th IEEE International On-Line Testing Symposium (IOLTS 2011), 49 (2011)

- M. Augustin, M. Gössel, R. Kraemer, Eine neue Fehlertoleranzmethode zur Verringerung des Flächenaufwandes von TMR-Systemen, Zuverlässigkeit und Entwurf, 4. GMM/GI/ITG-Fachtagung, (GMM-Fachbericht; 66), 89 (2010)

- M. Augustin, M. Gössel, R. Kraemer, Reducing the Area Overhead of TMR-Systems by Protecting Specific Signals, Proc. IEEE International On-Line Test Symposium 2010 (IOLTS 2010), (2010)

Diplomarbeiten/Masterarbeiten/Bachelorarbeiten

- Software Verification and Analysis of the NVIDIA Deep Learning Accelerator; F. Schmeller; Bachelor Thesis, Universität Potsdam, Germany (2021)

- A Multi-Tenancy Monitoring API for SAP Data Intelligence using the Prometheus Monitoring System; T. Bernhard; Bachelor Thesis, Universität Potsdam, Germany (2021)

- Implementierung eines Multi-Hop-Protokolls für die Kommunikation von Straßenlampen auf Grundlage einer Cross-Plattform; J. Rimatzki; Bachelor Thesis, Universität Potsdam, Germany (2019)

- Integration von Test- und Monitoring-Funktionalitäten in eine Sensorknoten-Middlewareplattform zur Durchführung von Tests in einem Sensornetz; P. Poppe; Master Thesis, Universität Potsdam, Germany (2019)

- Konzept und Implementierung einer Sensor-API in einem Betriebssystemabstraktionslayer für drahtlose Sensornetze; M. Hencke; Bachelor Thesis, Universität Potsdam, Germany (2019)

- Infrastruktur für verteilte Tests in drahtlosen Sensornetzen; S. Reinhold; Bachelor Thesis, Universität Potsdam, Germany (2018)

-

Ausbildung >> hier klicken <<

Das IHP blickt auf eine lange Tradition und viel Erfahrung beim Entwurf und der Fertigung drahtloser eingebetteter Systeme zurück. Diese Erfahrungen werden von den Mitarbeitern des IHP an die Studierenden der Universität Potsdam im Rahmen zahlreicher Lehrveranstaltungen im Bereich der Technischen Informatik weitergegeben. Dadurch erhalten die Studierenden das nötige Fachwissen, um später erfolgreich als Wissenschaftler in Projekten des IHP und der Universität Potsdam oder als Mitarbeiter in regional und global auf diesem Themenfeld agierenden Firmen tätig zu sein. Die angebotenen Lehrveranstaltungen umfassen unter anderem:

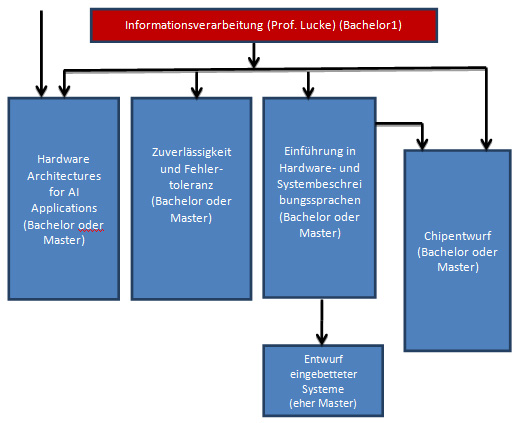

- Zuverlässigkeit und Fehlertoleranz

- Hardwarearchitekturen für KI-Anwendungen

- Entwurf eingebetteter Systeme

- Einführung in Hardware- und Systembeschreibungssprachen

- Chipentwurf

Die angebotenen Kurse beinhalten auch zahlreiche Praktika im Hardwarelabor. Entwurfs- und Entwicklungswerkzeuge für die Kurse werden durch das IHP bereitgestellt.

Die folgende Grafik zeigt einen Überblick über die angebotenen Kurse:

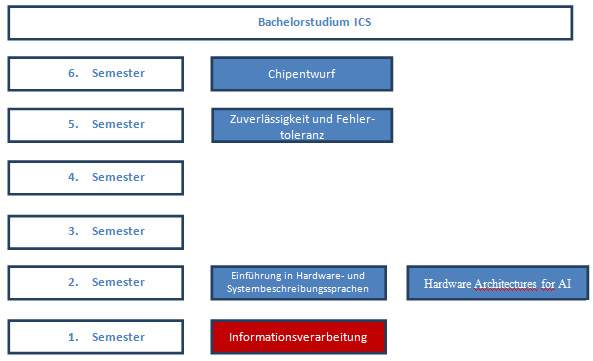

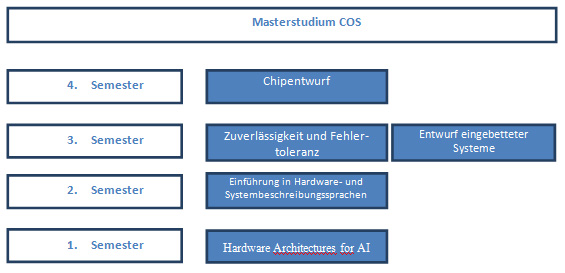

Eine mögliche und empfohlene Aufteilung der Kurse im Bachelor- (ICS) und Masterstudium (COS) zeigen die folgenden Grafiken: