Die Forschung der Gruppe zielt auf folgende Themen: Seitenkanal- und Manipulations-Angriffe; algorithmische und holistische Methoden zur Reduktion des Erfolges physikalischer Angriffe; Methodik zur Entwicklung von Designs, die gegen ein möglichst breites Spektrum physikalischer Angriffe resistent sind. Die Vision der Hardware Security Gruppe ist es, dass die Designer, die keine tiefe Kenntnisse im Bereich von Seitenkanal- und Fehlerinjektions-Angriffen haben, unter Anwendung einer „Security Optimization“-Option eines automatisierten Design-Tools die Schaltungen mit einer hohen Resistenz gegen mehrere physikalische Angriffe entwickeln können, was ein wichtiger Schritt zum Engineering resilienter Systeme ist.

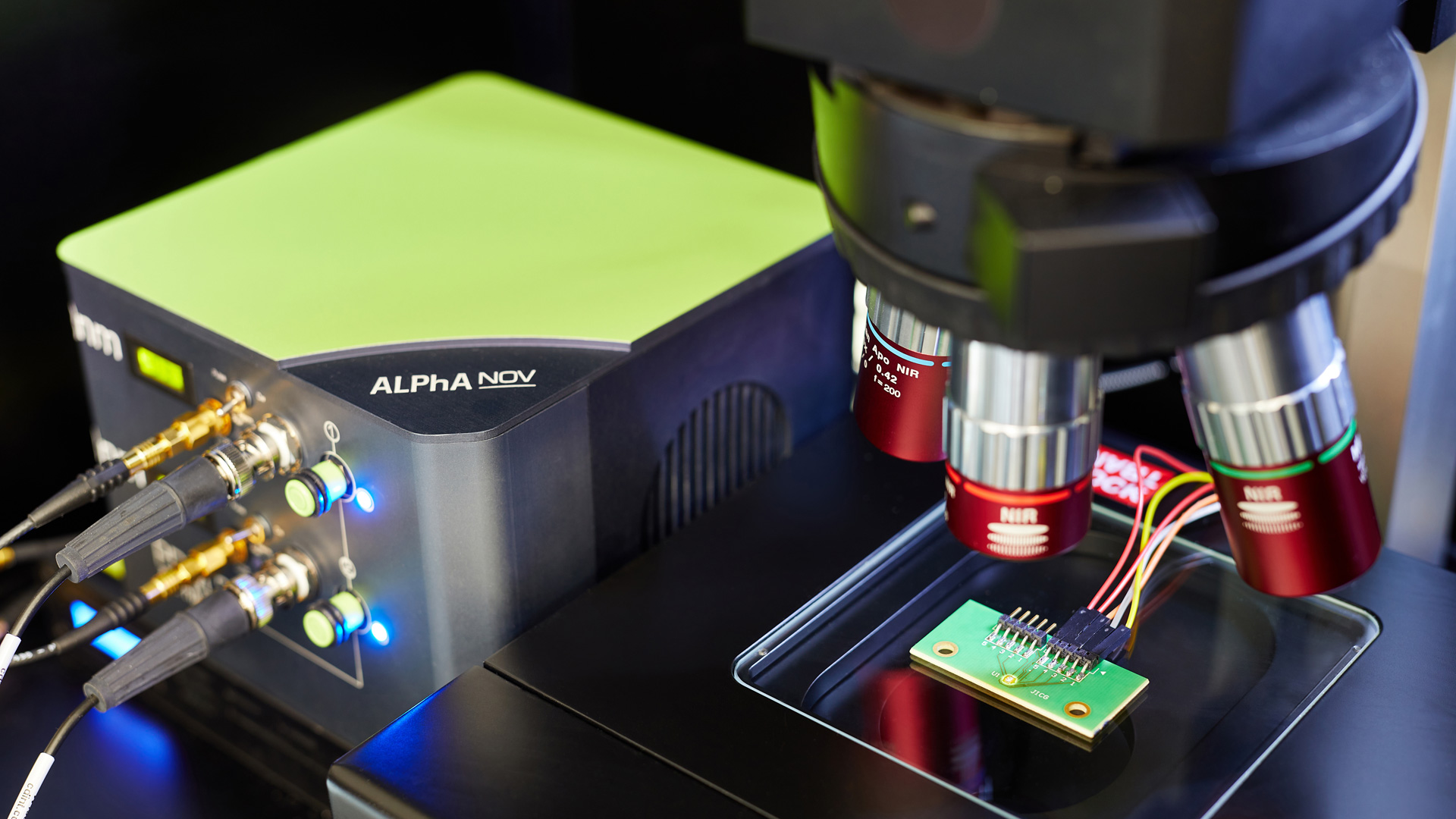

Kryptographische Algorithmen sind heutzutage das Hauptmittel für die Implementierung der Sicherheitsanforderungen. Es gibt viele standardisierte kryptographische Protokolle für Schlüsselaustausch, Verschlüsselung und Entschlüsselung der Daten, (gegenseitige) Authentifizierung, Generieren und Verfizieren digitaler Signaturen. Kryptographische Verfahren basieren auf komplexen mathematischen Operationen und sind deswegen oft in Hardware als spezialisierte ASICs implementiert, um die Ausführungszeit und den Energieverbrauch zu reduzieren. Die Wirksamkeit kryptographischer Verfahren basiert auf der Geheimhaltung von privaten Schlüsseln. Wenn potentielle Angreifer einen physikalischen Zugang zu den kryptographischen Implementierungen haben, können die kryptographischen ASICs mittels der so-genannten Seitenkanal-Analyse angegriffen werden, d.h. der Strom durch die kryptographischen ASICs, deren elektromagnetische Abstrahlung, die Ausführungszeit und viele andere Seitenkanal-Effekte können vom Angreifer gemessen und statistisch ausgewertet werden, um den verwendeten kryptographischen Schlüssel zu extrahieren. Eine andere Art der Angriffe ist die Manipulation der Funktionalität kryptographischer ASICs mittels Fehlerinjektionen. Außer kryptographischen Schaltungen fokussiert die Hardware Security Gruppe an der Untersuchungen der Manipulationsresistenz der RRAM Zellen. Die Methoden zur Erhöhung der Resistenz spielen eine signifikante Rolle bei Anwendung von RRAM-Strukturen als Hardware-Beschleuniger der Methoden Künstlicher Intelligenz. Ein wichtiger Ansatzpunkt ist die Resistenz der IHP RRAMs gegen Manipulationen, z. B. mittels optischen Fehlerinjektionen.

Die ersten Schritte auf diesem Weg sind das Sammeln, Analysieren, Überprüfen und Systematisieren möglicher „Teillösungs“-Erkenntnisse zur Reduktion des Erfolges physikalischer Angriffe. Systematisierte holistische Lösungen, Erkenntnisse und Kriterien werden die Basis einer Design-Methodik sein, die fürs Engineering der Designs, die gegen ein breites Spektrum von physikalischen Angriffen resistent sind, notwendig ist.

Hauptziele

Hauptziel

- Erarbeitung einer Design-Methodologie für die Entwicklung der Schaltungen mit einer hohen Resistenz gegen ein breites Spektrum physikalischer Angriffe

Forschungsthemen

- Hardwaresicherheit

- Seitenkanalangriffe und Gegenmaßnahmen

- effiziente Implementierung kryptographischer Verfahren in Hardware

- Anwendung der Methoden Künstlicher Intelligenz für Entwicklung resistenter Schaltungen

- Resistenz KI-Beschleunigern gegen physikalische Angriffe

Forschungsergebnisse

- Vulnerabilität von IHP-Logikgattern, JICG- und TMR-Register, und RRAM-Strukturen zu optischen FI demonstriert

- Abhängigkeit der Resistenz kryptographischer Designs von Taktfrequenz, Technologie, Gatter-Bibliothek, usw. demonstriert

- Vulnerabilität von regularity & atomicity principles zu den simple SCA Angriffen demonstriert, Gegenmaßnahmen vorgeschlagen