Diese Forschungsgruppe beschäftigt sich mit der Entwicklung von Funktionsmaterialien für die Mikroelektronik, die durch adaptive Implementierung in bereits existierende Si-basierte Technologien eine Vielfalt an Anwendungsgebiete und Herausforderungen der modernen Gesellschaft adressieren können. Durch die Gewinnung eines fundamentalen Verständnisses rund um die spezifischen Materialeigenschaften der Funktionsmaterialen, sowie der Erforschung innovativer Ansätze im Bereich ihrer Integration, des Bauteildesigns und der endgültigen systemischen Anwendung, bietet diese Forschungsrichtung potentielle und ausbaubare Lösungen im Rahmen des CMOS+X Kontextes an.

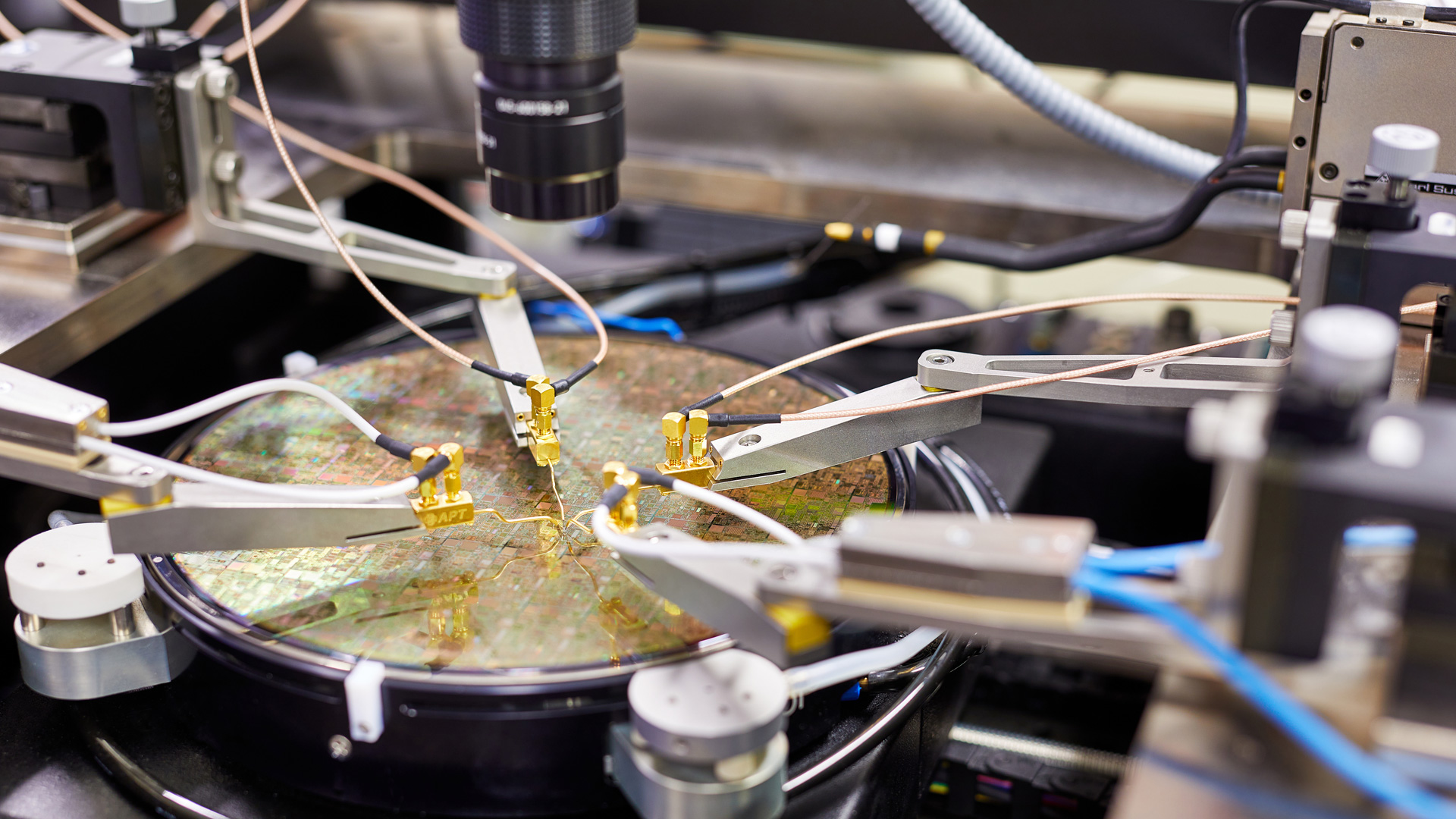

Um tiefergehendes Wissen zu erlangen, was zur präzisen Kontrolle der Eigenschaften dieser Materialsysteme und ihrer möglichen Integration erforderlich ist, nutzt unsere Gruppe synergetische Kompetenzen der theoretischen Modellierung in Kombination mit fortschrittlichen, hochmodernen experimentellen Techniken auf der Mikro- und Nanoskala.

Forschungsziele

- Weiterentwicklung, Charakterisierung und Modellierung von memristiven Bauelementen für nichtflüchtige Speicher, sowie deren Schaltungen und Algorithmen zur Anwendung in neuronalen Netzwerken und im Edge Computing

- Entwicklung und Integration von plasmonischen und dielektrischen Nahfeldsensoren des VIS/IR- und THz-Bereichs für hyperspektrale Bildgebung, medizinischen Diagnostik, Industrie-/Umweltmonitoring und Biofunktionalisierung

- Integration von III/V-Verbindungshalbleitermaterialien auf die etablierte CMOS-kompatible Siliziumtechnologieplattform für elektronische und photonische Bauelementkonzepte und -systeme

- Verständnis technologischer Probleme im Zusammenhang mit Defekten in Materialien und Bauelemente der Mikroelektronik und Photonik

Forschungsschwerpunkte

Die Diversität der Forschungsschwerpunkte und -themen in dieser Arbeitsgruppe verbildlicht das große Interesse, das immense Potential und die vielen Möglichkeiten, welche Funktionsmaterialien in der Verbesserung bereits existierende Technologien und in der Entwicklung neuer Bauteilkonzepte besitzen. Hierbei achten wir stets darauf, dass neue technologische Vorstöße in diesem Rahmen immer mit einer adaptiven Implementierung zu bereits etablierten Technologieplattformen vollzogen werden, um der Forschungsgemeinschaft und der Gesellschaft eine schnelle, effiziente und qualifizierte Bereitstellung unserer Lösungen zu ermöglichen.

Memristive Bauelemente weisen eine variable widerstandsbasierte Speicherfunktion auf. Von besonderem Interesse ist diese Art von Bauelementen als schaltbares Element für nichtflüchtige RRAM-Speicher, aber auch für den Bereich der analogen neuronalen Schaltungstechnik bzw. energieeffizientes In-Memory Computing. Hier eröffnen die memristiven Bauelemente die Möglichkeit, derzeitig bestehenden Hürden digitaler Datenverarbeitung im Bereich kognitiver Aufgabenstellungen zu überwinden. Im Mittelpunkt unseres Forschungsschwerpunktes „Neuronale Netzwerke“ steht die Entwicklung der memristiven Bauelemente auf Al:HfO2-Basis für zukünftige elektronische Schaltungen mit starker Orientierung an biologischen Systemen. Darauf aufbauend entwerfen wir KI-Lösungen als vielversprechendster Ansatz zur Beherrschung komplexer Aufgaben, wie etwa Bild-, Objekt- und Szenenerkennung, oder Regelung dynamischer, nichtlinearer Systeme für Anwendungsgebiete, wie z.B. E-Mobilität, Aerospace, Datenverarbeitung und Sensorkontrolle. Um die Funktionsfähigkeit von Memristive Bauelemente innerhalb eines intelligenten In-Memory-Computing-Konzepts unter extremen Umwelteinflüssen zu verstehen und am Ende auch zu gewährleisten, untersuchen wir ebenfalls die Auswirkungen von Strahlung und kyrogenischen Temperaturen auf unsere etablierten memristiven Bauelemente und ihre Systemarchitektur.

Die starke Evolution hin zu einer immer digitalisierten Gesellschaft und Industrie hat die Nachfrage nach modernen Sensorlösungen in neue Höhen steigen lassen. Im Mittelpunkt unseres Forschungsschwerpunktes „Sensorik“ steht die Entwicklung von plasmonischen, dielektrischen und photoakustischen Sensorsystemen für mannigfaltige Anwendungsbereichs des täglichen Lebens. Unter diese Prämisse untersuchen wir Biosensoren basierend auf Plasmonenresonanzen, welche zu den sensibelsten Methoden gehören, um Veränderungen der Ordnung eines einzelnen Biomoleküls nachzuweisen. Hierzu wurden kürzlich mit der BTU Cottbus-Senftenberg die ersten plasmonischen Sensoren entwickelt und getestet, um Krankheiten von Nutzpflanzen frühzeitig erkennen zu können. Die Energiewende in der Lausitz-Region wandelt das traditionelle Kohlerevier zur Modellregion der Wasserstoffstrategie, wobei (Kohlen-)Wasserstoffe (synthetische Kraftstoffe) als wichtige Energieträger der Zukunft für stationäre und mobile Anwendungen gelten. Um den einhergehenden enormer Bedarf an leistungsfähigen Sensoren für die sicherheitsrelevante Überwachung der fluiden Kraftstoffe zu bedienen, beteiligen wir uns im Rahmen des Projektes iCampms 2.0 an der Entwicklung moderner dielektrischer (Kohlen-)wasserstoff-Sensoren. Des Weiteren engagieren wir uns im ebenfalls an der BTU Cottbus-Senftenberg lokalisierten BMBF-Verbundvorhaben OASYS an der Entwicklung von metaoberflächen-basierten dielektrischen Nahfeldsensoren für eine Vielzahl innovativer Anwendungen z.B. im Bereich der hyperspektrale Bildgebung, medizinischen Diagnostik, aber auch der industriellen Fertigung und modernen Agrar-/Umweltwirtschaft.

Die kontinuierliche Skalierung und Entwicklung von rein Silizium-basierten mikroelektronischen Bauelementen erreicht mehr und mehr ihre Grenzen. Verbindungshalbleiter der Gruppe III/V haben sich mittlerweile als vielversprechende Kandidaten herauskristallisiert, aufgrund ihrer überlegenen Eigenschaften (bei z.B. Ladungsträgerbeweglichkeit und der Fähigkeit, Bandlücken zu erzeugen), diese Grenzen zu überwinden. Dies macht die III/V-Verbindungshalbleiter interessant sowohl für den Einsatz in elektronischen Bauteilen, als auch in aktiven photonischen Bauelementen und in der Quantentechnologie. Im Mittelpunkt unseres Forschungsschwerpunktes „III/V-on-Si“ steht eine angestrebte Ko-Integration von III/V-Materialien auf-Silizium, um hochleistungsfähige, kostengünstige Systeme zu ermöglichen, welche die vorteilhaften III/V-Eigenschaften und -Funktionen mit der ausgereiften Mainstream-Silizium-Fertigungstechnologie kombinieren. In diesem Rahmen sind wir bestrebt, III/V-Materialien, Prozesse und Bauelemente in der neuen, von der FMD-finanzierten Versuchsprozesslinie im Reinraum für die künftige Umsetzung in einem CMOS+X-kompatiblen Kontext zu erforschen.