This research group is working on the development of functional materials for microelectronics that can address a wide range of applications and challenges in today´s society through adaptive implementation in already existing Si-based technologies. By gaining a fundamental understanding of the specific material properties of functional materials, as well as by exploring innovative approaches to their integration, device design and final system application, this research direction offers potential and extendable solutions in the CMOS+X context.

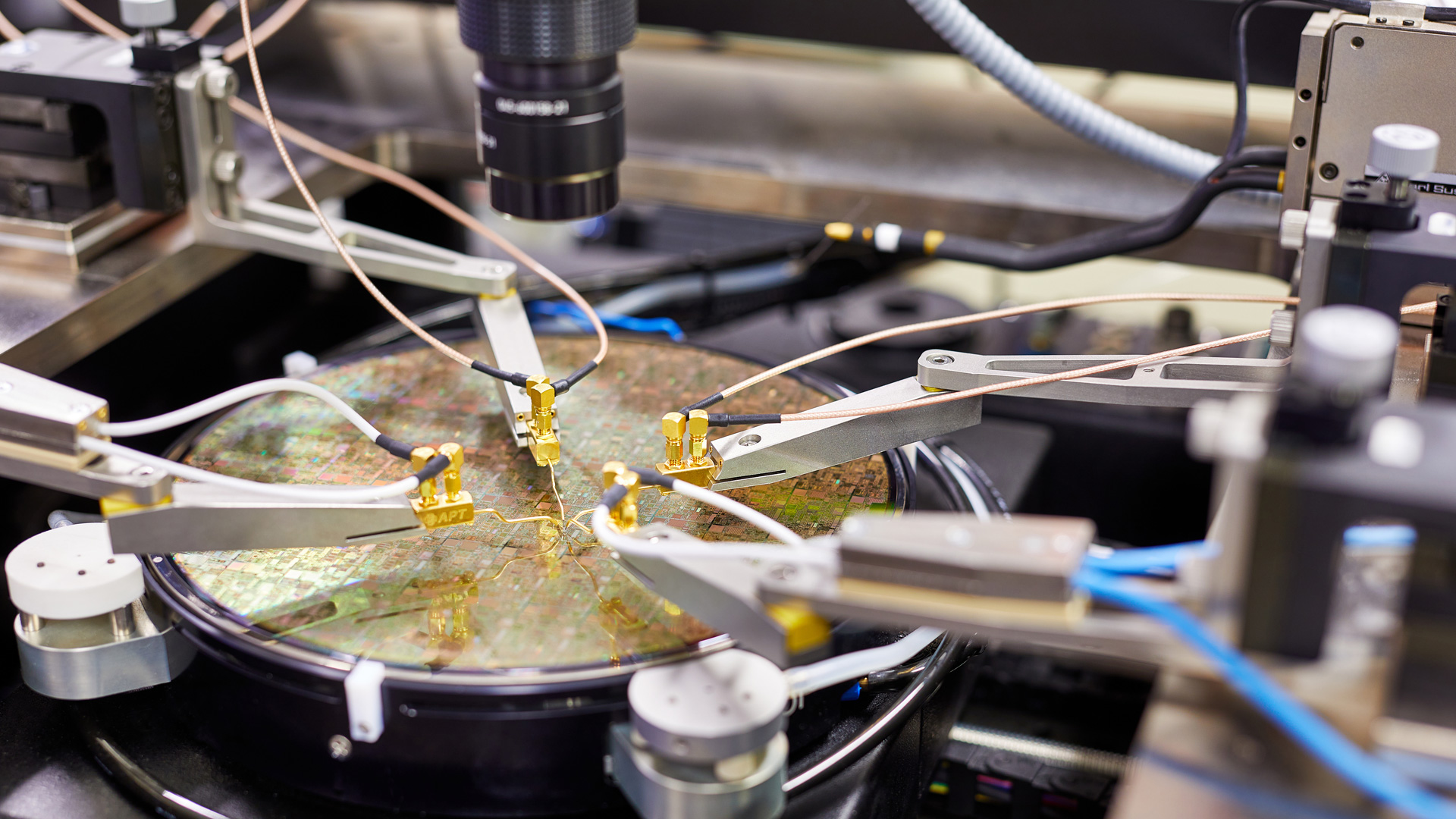

To obtain a deeper knowledge of what is needed to precisely control the properties of these material systems and their possible integration, this group uses synergistic competencies in theoretical modeling combined with advanced, state-of-the-art experimental techniques on the micro- and nanoscale.

Main targets

- Further development, characterization and modeling of memristive devices for non-volatile memories, as well as their circuits and algorithms for application in neural networks and edge computing

- Development and integration of plasmonic and dielectric near-field sensors in the VIS/IR and THz range for hyperspectral imaging, medical diagnostics, industrial/environmental monitoring and biofunctionalization

- Integration of III-V compound semiconductor materials on the established CMOS-compatible silicon technology platform for electronic and photonic device concepts and systems

- Understanding of technological problems related to defects in materials and devices in microelectronics and photonics

Research topics

The diversity of research topics and subjects in this working group illustrates the great interest, the immense potential and the many possibilities that functional materials offer for improving existing technologies and developing new component concepts. In this context, we always seek to ensure that new technological advances go hand in hand with an adaptive implementation in established technology platforms, in order to provide our solutions to the research community and society in a fast, efficient and qualified manner.

Memristive components exhibit a variable resistance-based memory function. These components are of particular interest as a switchable element for non-volatile RRAM memories, but also for the field of analog neural circuit technology and energy-efficient in-memory computing. Here, memristive components offer the possibility of overcoming the current obstacles of digital data processing in the area of cognitive functions. At the center of our research focus “Neural Networks” is the development of memristive devices based on Al:HfO2 for future electronic circuits with a strong orientation towards biological systems. Based on this, we design AI solutions as the most promising approach for mastering complex tasks, such as image, object and scene recognition, or controlling dynamic, nonlinear systems for application areas such as e-mobility, aerospace, data processing and sensor control. In order to understand and finally ensure the functionality of memristive devices within an intelligent in-memory computing concept under extreme environmental conditions, we are also investigating the effects of radiation and cryogenic temperatures on our established memristive devices and their system architecture.

The strong evolution towards an increasingly digitized society and industry has driven the demand for modern sensor solutions to new heights. At the center of our research focus “Sensors” is the development of plasmonic, dielectric and photoacoustic sensor systems for a wide range of applications in everyday life. Under this premise, we are investigating biosensors based on plasmon resonance, which is one of the most sensitive methods for detecting changes in the structure of a single biomolecule. Recently, the our first plasmonic sensors have been developed and tested with the BTU Cottbus-Senftenberg to detect diseases of agricultural crops at an early stage. The energy transformation in the Lausitz region is turning the traditional coalfield region into a model region for the hydrogen strategy, with (carbon) hydrogen (synthetic fuels) being considered an important energy source of the future for stationary and mobile applications. In order to meet the enormous demand for high-performance sensors for the safety-relevant monitoring of liquid fuels, we are participating in the development of modern dielectric hydrogen (-carbon) sensors as part of the iCampms 2.0 project. Furthermore, we are also engaged in the BMBF joint project OASYS, which is also located at the BTU Cottbus-Senftenberg, for the realization of meta-surface-based dielectric near-field sensors for a variety of innovative applications, e.g. in the field of hyperspectral imaging, medical diagnostics, but also in industrial production and modern agriculture/environmental industries.

The continuous scaling and development of purely silicon-based microelectronic devices is gradually reaching its physical limits. Group III-V compound semiconductors have emerged as promising candidates to overcome these limitations due to their superior properties (e.g. in carrier mobility and ability to create band gaps). This makes III-V semiconductors interesting for use in electronic devices, as well as in active photonic components and in quantum technology. At the center of our research focus “III/V-on-Si” is the objective of co-integrating III-V materials on silicon to enable high-performance, low-cost systems that combine the advantageous III-V properties and functions with the mature mainstream silicon manufacturing technology. In this context, we are committed to researching III-V materials, processes and devices using our new FMD-funded exploratory process line in our clean room for future realization in a CMOS+X-compatible context.