The research group on the subject of Fault Tolerant Computing, as part of the system architecture department, aims to investigate different methods for mitigating aging and error effects and to implement them at the system level. It thus forms the bridge between the pure development of state-of-the-art systems and their usage in safety-critical applications with high demands on reliability.

Main targets

- development of fault tolerant systems for application areas such as industrial automation, automotive, aerospace

- mitigation of process fluctuations for RRAM-based PIM and design of RRAM-based systems

- support of systems based on open source hardware

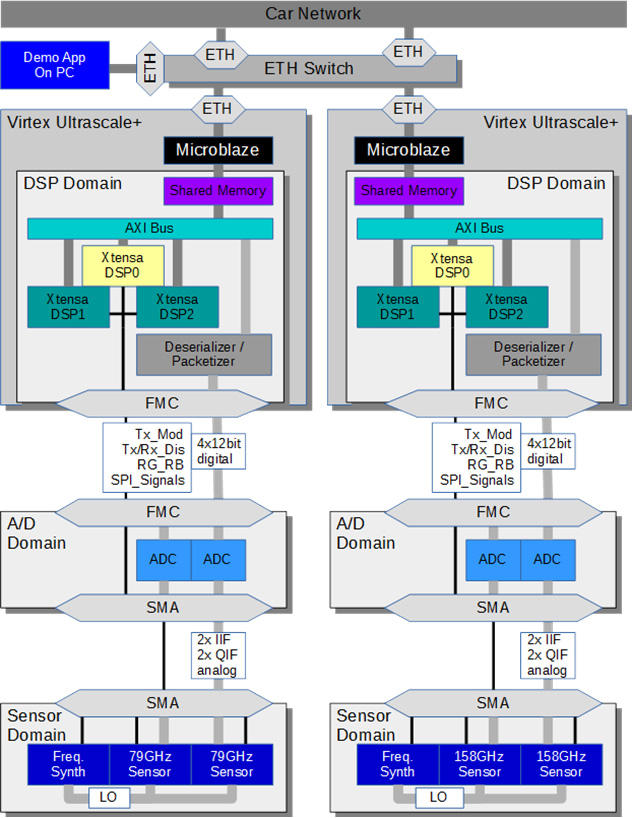

- optimized baseband and sensor data processing in safety-critical applications

Research topics

- heterogeneous computing for AI applications

- reliability modelling of AI applications

- AI methods for system reconfiguration

- sensing of IC condition

- adaptive fault tolerant (multi-) processors

- DSP and AI data evaluation for radar applications

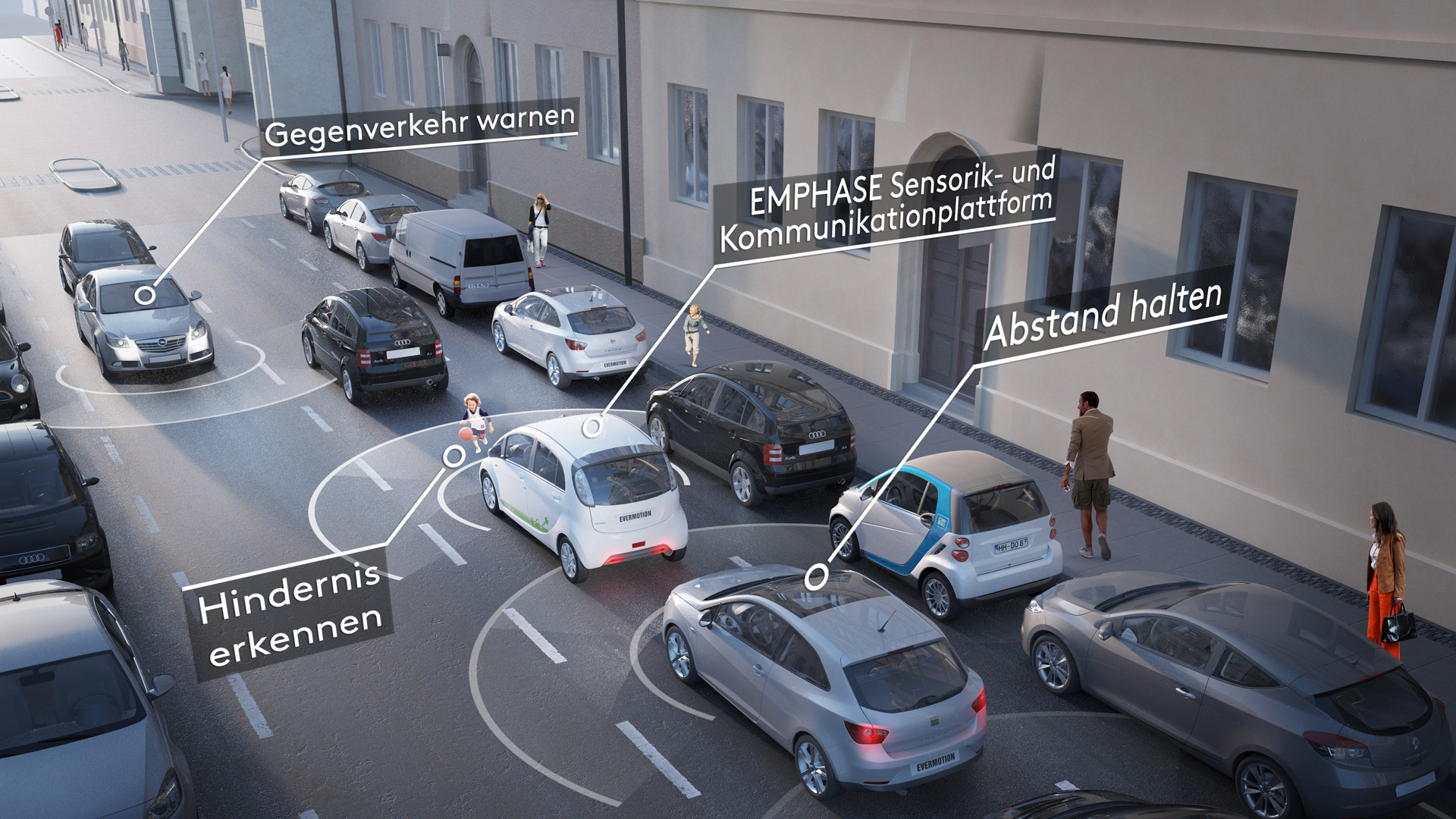

For some years now, highly automated, processor-based systems have been finding their way into many areas of the private and professional environment. Since they are entrusted with increasingly important tasks, some of which affect the well-being or health of the users, they have to meet increasing demands.

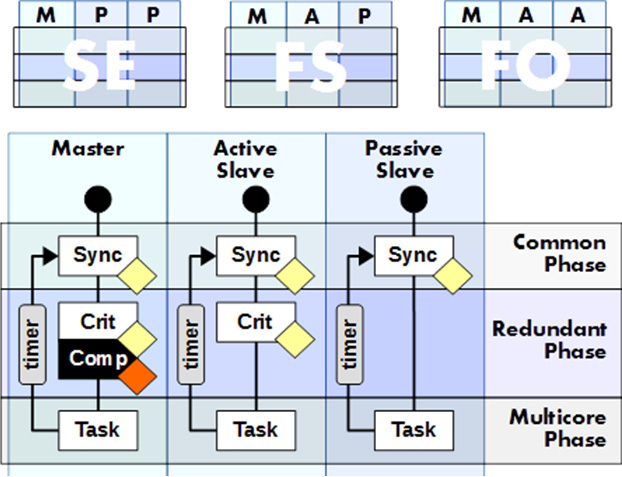

For this reason, we develop systems in our projects that are geared towards the quality and performance requirements of current and future fields of application. The main focus here is the development of fault-tolerant systems. In EMPHASE and Scale4Edge, for example, we develop special multi-core processors that perform software- or hardware-based operations redundantly and thus correct errors in individual cores. So that this additional effort only arises in critical situations, we rely on the information from aging and radiation sensors and additionally reduce the sensitivity of the ICs through a radiation-hard design.

We meet the highest performance requirements through the use of multi-core systems and the implementation of hardware accelerators on FPGA or even as IC. In order to remain competitive in the future, we are testing the use of technologies that are still in the development stage, such as ReRAMs in the KI-PRO project, which are implemented using in-memory computing accelerators for AI applications.

In addition, we rely heavily on open source hardware when developing our processors. This is not only interesting from a cost and research point of view, but also opens up a diverse portfolio of tailor-made solutions that are not limited by export restrictions and are therefore available to the general public.