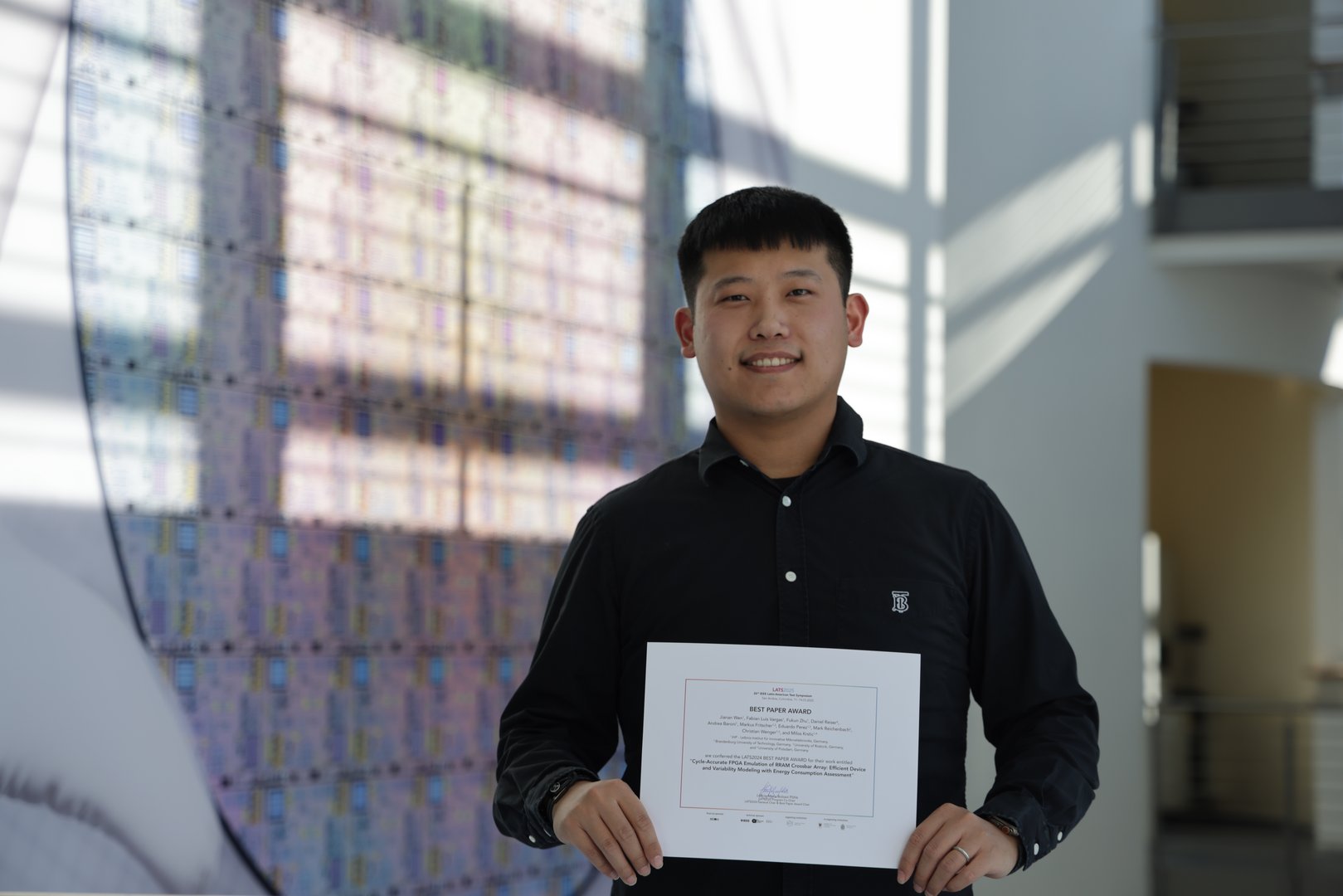

IHP scientists, along with researchers from Brandenburg University of Technology, University of Rostock, and University of Potsdam, won the best paper award at the 26th IEEE Latin American Test Symposium (LATS) 2025, held from March 11-14, in San Andrés Island, Colombia. The LATS is a recognized forum dedicated to presenting and discussing scientific results, emerging ideas, applications, hot topics and new trends in the area of electronic-based circuits and system testing, reliability, and security.

The paper, titled “Cycle-Accurate FPGA Emulation of RRAM Crossbar Array: Efficient Device and Variability Modeling with Energy Consumption Assessment” addresses actual challenges in electronic design automation (EDA). One of the key gaps here is the lack of support for rapid prototyping, design space exploration, and system-level simulations that account for process-dependent device variability. To address this, the joint research between IHP, BTU, Uni Rostock, and Uni Potsdam introduces an FPGA-based emulation approach for RRAM crossbars, enabling real-time, cycle-accurate emulations without complex device models. By leveraging pre-generated look-up tables, the group captures RRAM behavior with high accuracy, while a multivariate kernel density estimation (KDE) method is used to model device variability. This approach enables precise latency determination and, when combined with NeuroSim, allows for energy consumption estimation - offering a significant speedup over traditional behavioral simulations.

Special Congratulations to IHP team: Jianan Wen, Fabian Luis Vargas, Andrea Baroni, Markus Fritscher, Eduardo Perez, Christian Wenger, and Milos Krstic!

The paper can be found here: https://ieeexplore.ieee.org/document/10534601